Part 9: The 2020 Wilson Research Group Functional Verification Study

IC/ASIC Verification Technology Adoption Trends

This blog is a continuation of a series of blogs related to the 2020 Wilson Research Group Functional Verification Study. In my previous blog, I focused on IC/ASIC design project resource trends. In this blog I examine IC/ASIC project verification technology adoption trends.

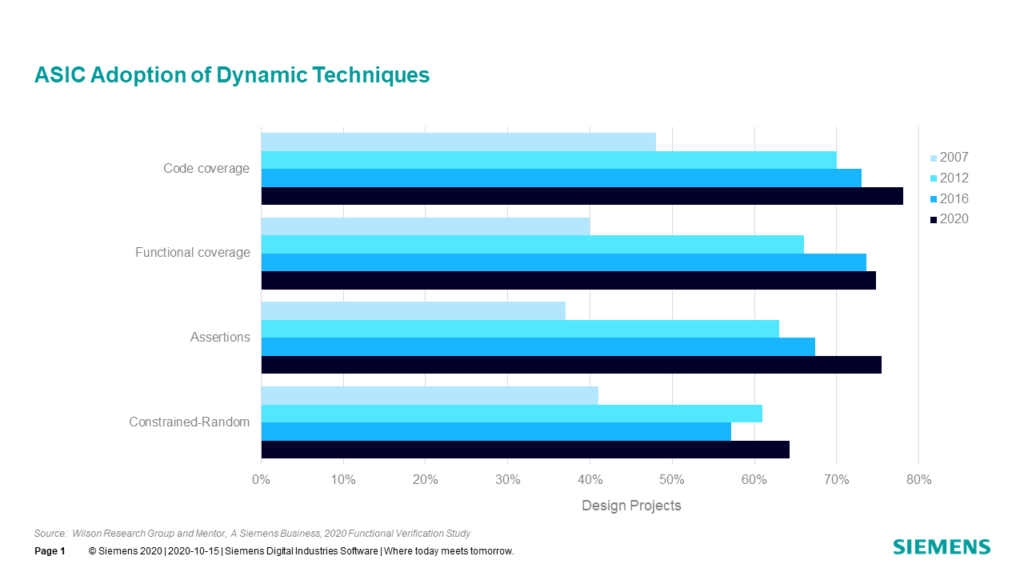

Dynamic Verification Techniques

The IC/ASIC market in the mid-2000 timeframe underwent growing pains to address increased verification complexity, predominately brought on with the adoption of SoC-class designs. This maturing of IC/ASIC projects’ processes is clearly visible when comparing various simulation-based verification technology adoption trends from 2007 through 2020 as shown in Figure 9-1.

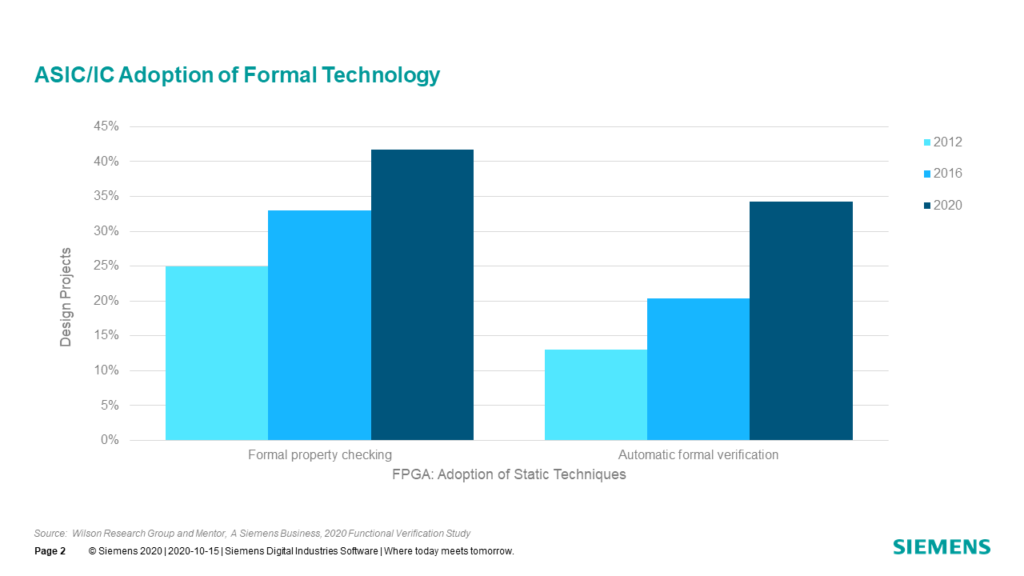

IC/ASIC Static Verification Techniques

Figure 9-2 shows the IC/ASIC adoption trends for formal property checking (e.g., model checking), as well as automatic formal applications. Examples of automatic formal application tools include: SoC integration connectivity checking, deadlock detection, X semantic safety checks, coverage reachability analysis, and many other properties that can be automatically extracted and then formally proven.

We see in Figure 9-2 that formal property checking has grown at a 6.7% CAGR since 2012, while automatic formal applications has grown at a 12.8% CAGR.

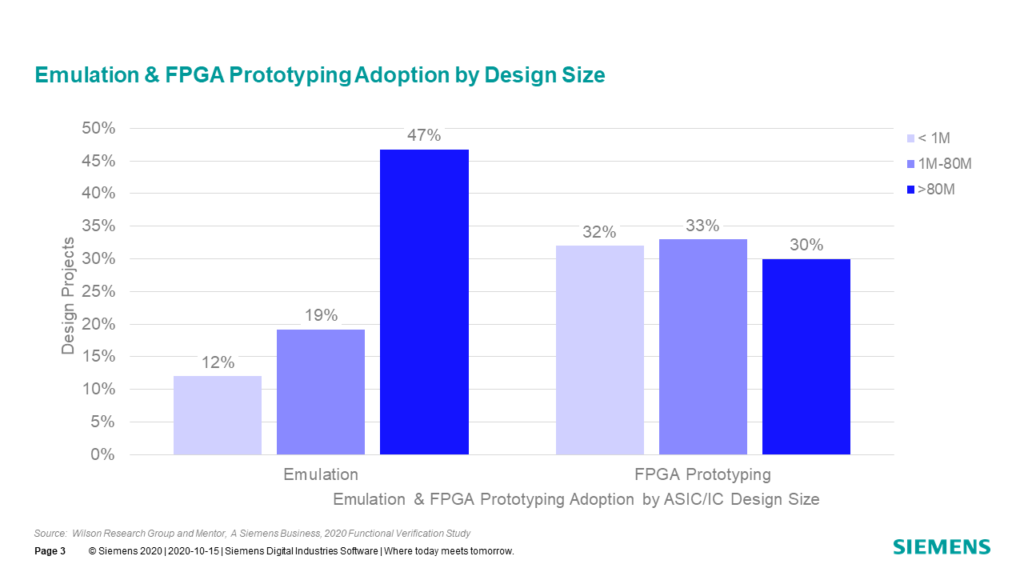

Emulation and FPGA Prototyping

ESDA categorizes emulation and FPGA under “Other Logic Verification,” separate from logic simulation. They estimated the market value of this category at $650.6M in 2019. Various analyst expect this category to grow in the order of 8-10% CAGR by 2024.

Historically, the simulation market has depended on processor frequency scaling as one means of continual improvement in simulation performance. However, as processor frequency scaling leveled off in the mid-2000 timeframe, simulation-based techniques were unable to keep up with today’s growing complexity. This is particularly true when simulating large designs that include both software and embedded processor core models. Hence, acceleration techniques are now required to extend SoC verification performance for very large designs. In fact, emulation and FPGA prototyping have become key platforms for SoC integration verification where both hardware and software are integrated into a system for the first time. In addition to SoC verification, emulation and FPGA prototyping are also used today as a platform for software development.

Taking a deeper dive into the data we collected from this year’s study, we decided to partitions the data for emulation and FPGA prototyping adoption by design size as follows: less than 1M gates, 1M to 80M gates, and greater than 80M gates, as shown in Figure 9-3. Notice that the project adoption of emulation continues to increase as design sizes increase. However, the adoption of FPGA prototyping does not follow a similar trend as design sizes increase beyond 80M gates.

It’s important to note that the percentage of project adoption of either emulation or FPGA prototyping shown in Figure 9-3 doesn’t necessarily correlate to market size in terms of revenue. That is, adoption of these technologies by a projects doesn’t reveal how much adoption (e.g., how many emulators or FPGA prototyping systems were acquired by the project).

In my next blog I plan to discuss various IC/ASIC language and library adoption trends.

Quick links to the 2020 Wilson Research Group Study results

- Prologue: The 2020 Wilson Research Group Functional Verification Study

- Understanding and Minimizing Study Bias (2020 Study)

- Part 1 – FPGA Design Trends

- Part 2 – FPGA Verification Effectiveness Trends

- Part 3 – FPGA Verification Effort Trends

- Part 4 – FPGA Verification Effort Trends (Continued)

- Part 5 – FPGA Verification Technology Adoption Trends

- Part 6 – FPGA Verification Language and Library Adoption Trends

- Part 7 – IC/ASIC Design Trends

- Part 8 – IC/ASIC Resource Trends

- Part 9 – IC/ASIC Verification Technology Adoption Trends

- Part 10 – IC/ASIC Language and Library Adoption Trends

- Part 11 – IC/ASIC Power Management Trends

- Part 12 – IC/ASIC Verification Results Trends

- Conclusion: The 2020 Wilson Research Group Functional

- Epilogue: The 2020 Wilson Research Group Functional Verification Study

Comments

Leave a Reply

You must be logged in to post a comment.

Always good information, but I think Figure 9-2 is mislabeled at the bottom. Should be “ASIC: Adoption of Static Techniques” (??)