Part 5: The 2020 Wilson Research Group Functional Verification Study

This blog is a continuation of a series of blogs related to the 2020 Wilson Research Group Functional Verification Study. In my previous blog, I discussed verification effort trends specifically focused on where FPGA design and verification engineers spend their time. In this blog I present verification techniques and technologies adoption trends, as identified by the 2020 Wilson Research Group study.

FPGA Verification Technology Adoption Trends

An interesting trend we see in the FPGA space is a continual maturing of its functional verification processes. In fact, we find that the FPGA design space is about where the ASIC/IC design space was about seven years ago in terms of pre-lab verification maturity—and it is catching up quickly. A question you might ask is, “What is driving this trend?” In Part 1 of this blog series I showed rising design complexity with the adoption of more advanced FPGA designs, as well as multiple embedded processor architectures targeted at FPGA designs. In addition, I’ve presented trend data that shows an increase in total project time and effort spent in verification (Part 3 and Part 4).

To address growing verification complexity, we find that many FPGA projects are starting to mature their pre-lab functional verification processes. In this section, we present FPGA trends related to the adoption of various verification techniques, which are fairly standard practice today on most IC/ASIC projects.

FPGA Simulation Technique Adoption Trends

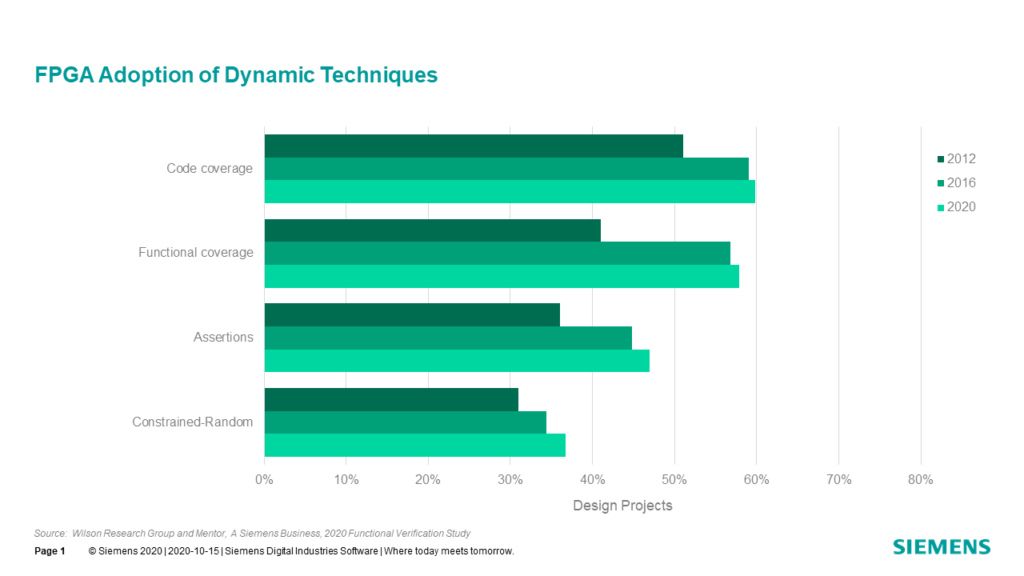

Fig. 5-1 shows the FPGA project adoption trends for various simulation-based techniques from 2012 through 2020, which include code coverage, functional coverage, assertions, and constrained-random simulation. Notice the increased adoption of these various techniques throughout this period.

FPGA Formal Technology Adoption Trends

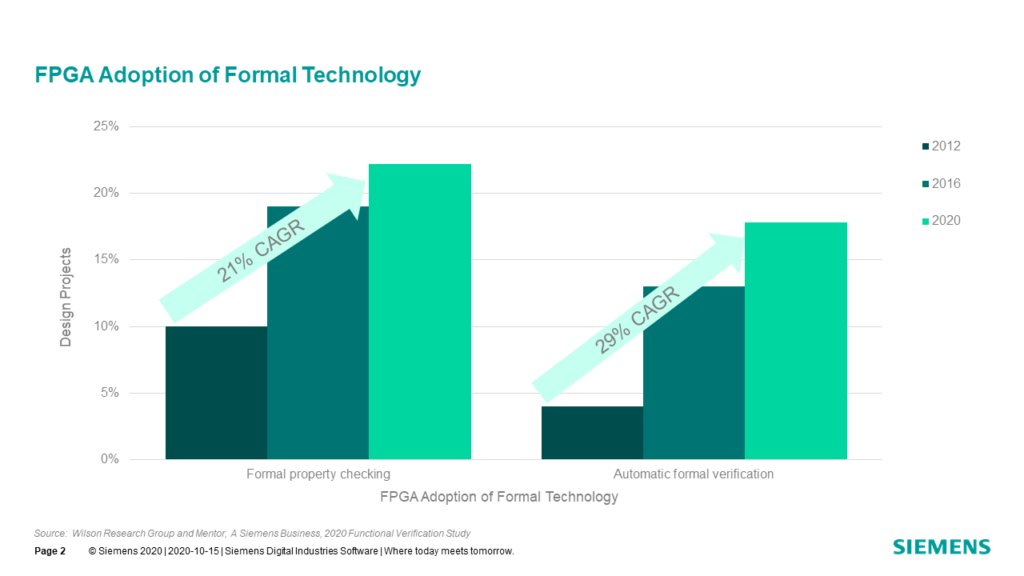

The adoption trends for formal property checking (e.g., model checking) and automatic formal applications are shown in Fig. 5-2. We found that the adoption of formal property checking on FPGA projects is growing at an impressive 21% CAGR, and the adoption of automatic formal applications is growing at a 29% CAGR. Historically, the formal property checking process has required specialized skills and expertise. However, the recent emergence of automatic formal applications provides narrowly focused solutions and does not require specialized skills for adoption. In general, formal solutions (i.e., formal property checking combined with automatic formal applications) are one of the fastest growing segments in functional verification.

The key observation from these adoption trends is that the FPGA market has matured its verification processes, as I previously stated. This maturity is likely due to the growing complexity of designs as discussed in my previous blogs.

In my next blog, I’ll focus on FPGA design and verification language adoption trends, as identified by the 2020 Wilson Research Group study.

Quick links to the 2020 Wilson Research Group Study results

- Prologue: The 2020 Wilson Research Group Functional Verification Study

- Understanding and Minimizing Study Bias (2020 Study)

- Part 1 – FPGA Design Trends

- Part 2 – FPGA Verification Effectiveness Trends

- Part 3 – FPGA Verification Effort Trends

- Part 4 – FPGA Verification Effort Trends (Continued)

- Part 5 – FPGA Verification Technology Adoption Trends

- Part 6 – FPGA Verification Language and Library Adoption Trends

- Part 7 – IC/ASIC Design Trends

- Part 8 – IC/ASIC Resource Trends

- Part 9 – IC/ASIC Verification Technology Adoption Trends

- Part 10 – IC/ASIC Language and Library Adoption Trends

- Part 11 – IC/ASIC Power Management Trends

- Part 12 – IC/ASIC Verification Results Trends

- Conclusion: The 2020 Wilson Research Group Functional

- Epilogue: The 2020 Wilson Research Group Functional Verification Study

Comments