Part 10: The 2020 Wilson Research Group Functional Verification Study

IC/ASIC Language and Library Adoption Trends

This blog is a continuation of a series of blogs related to the 2020 Wilson Research Group Functional Verification Study. In my previous blog, I examined IC/ASIC project verification technology adoption trends. In this blog I plan to discuss various IC/ASIC language and library adoption trends.

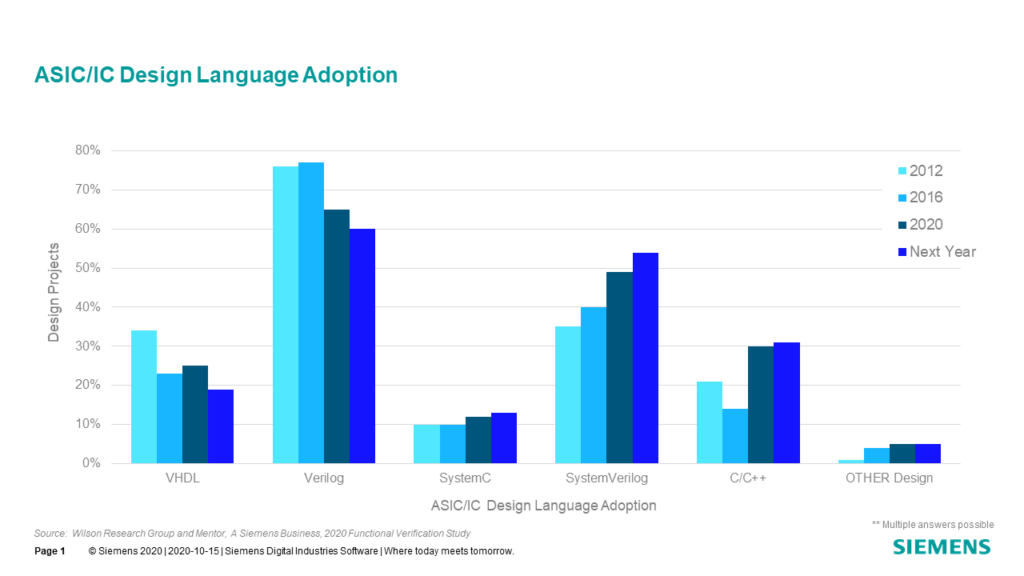

Figure 10-1 shows the aggregated adoption trends for languages used to create RTL designs across all market segments and all regions of the world. We see continual interest in SystemVerilog for RTL creation.

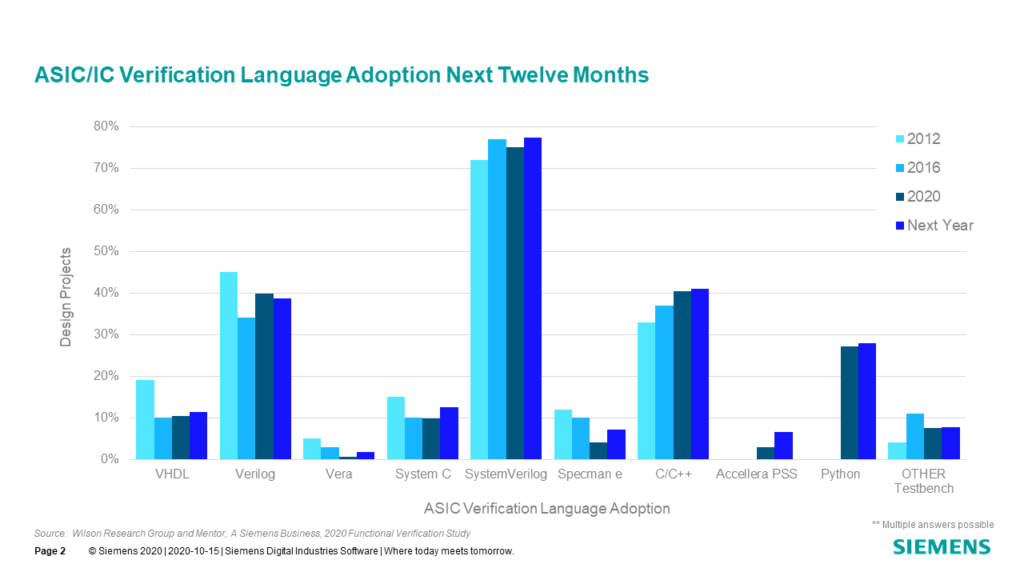

In Figure 10-2, we show the adoption trends for languages to build testbenches. It is not uncommon for IC/ASIC projects to use multiple languages when constructing their testbenches, which is why the percentage adoption sums to more than 100 percent. This practice of adopting multiple languages is often due to legacy code as well as purchased verification IP written in a different language.

In the 2020 data, we continue to see an increase in adoption of C/C++ for testbench development. In addition, we show the adoption levels for the Accellera Portable Test and Stimulus Standard (PSS). Finally, in 2020, for the first time, we explicitly asked about the adoption of Python for testbench development.

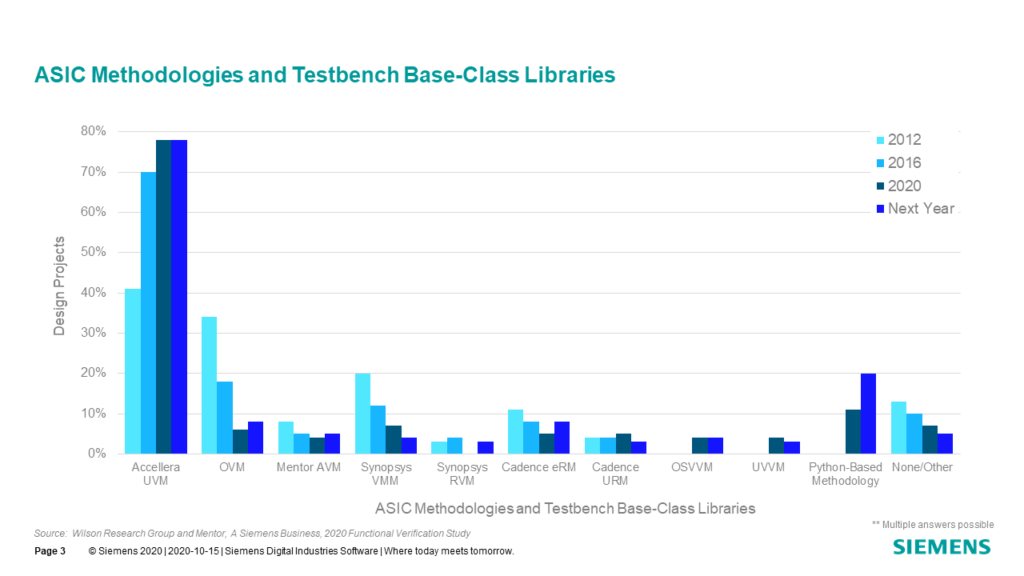

The adoption trends for various base-class library and methodology standards are shown in Figure 10-3. We found that the Accellera UVM is currently the predominant standard that has been adopted to create IC/ASIC testbenches, and it continues to grow. In 2018, we first started tracking the Open Source VHDL Verification Methodology™ (OSVVM) and the Universal VHDL Verification Methodology (UVVM), and we plan to show trends in our future studies. In addition, for the 2020 study, we are tracking Python-based methodologies, such as cocotb, for the first time.

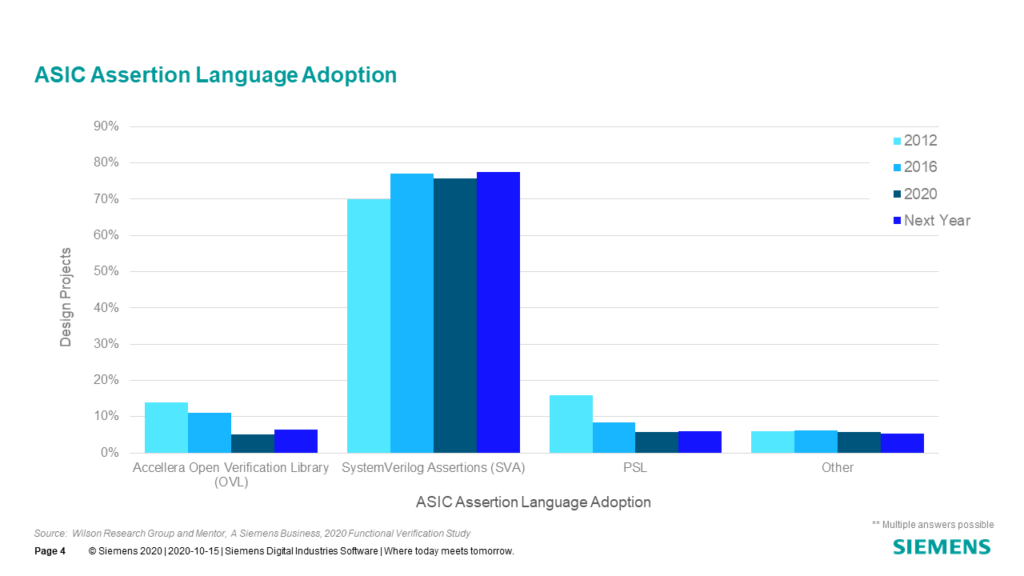

Finally, IC/ASIC project adoption trends for various assertion language standards are shown in Figure 10-4. SystemVerilog Assertions (SVA) is the predominant assertion language in use today. Similar to languages used to build testbenches, it is not unusual to find IC/ ASIC projects create their RTL in VHDL and then create their assertions using SVA.

In my next blog I plan to present the IC/ASIC design and verification power trends.

Quick links to the 2020 Wilson Research Group Study results

- Prologue: The 2020 Wilson Research Group Functional Verification Study

- Understanding and Minimizing Study Bias (2020 Study)

- Part 1 – FPGA Design Trends

- Part 2 – FPGA Verification Effectiveness Trends

- Part 3 – FPGA Verification Effort Trends

- Part 4 – FPGA Verification Effort Trends (Continued)

- Part 5 – FPGA Verification Technology Adoption Trends

- Part 6 – FPGA Verification Language and Library Adoption Trends

- Part 7 – IC/ASIC Design Trends

- Part 8 – IC/ASIC Resource Trends

- Part 9 – IC/ASIC Verification Technology Adoption Trends

- Part 10 – IC/ASIC Language and Library Adoption Trends

- Part 11 – IC/ASIC Power Management Trends

- Part 12 – IC/ASIC Verification Results Trends

- Conclusion: The 2020 Wilson Research Group Functional

- Epilogue: The 2020 Wilson Research Group Functional Verification Study

Comments