DAC in December?? A Review of Calibre Design Solutions at DAC 2021

Did it feel a bit weird to be submitting research papers for DAC 2022 while packing to go to DAC 2021 (or logging on virtually)? If so, you’re not alone. The shift from June to December left a lot of folks reshuffling their calendars, including us! And while the physical attendance may have been lighter than in the past, there was plenty of interest in the innovative tools and technologies available from Calibre Design, both in person and virtually!

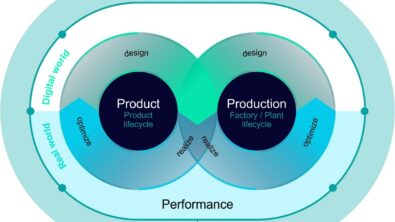

As usual, Joseph Sawicki, executive vice president of Siemens EDA, was in demand for his insights and predictions on the semiconductor industry. Joe’s presentation, Digitalization—The Return to Outsize Growth for the Semiconductor Industry, examined the intense expansion of digitalization across all industry over the past year, fueled and enabled by innovation in the semiconductor industry. Looking ahead, Joe sees no signs of this trend slowing any time soon. To the contrary, he expects technologies such as IoT, artificial intelligence, and cloud computing, coupled with new computing and telecom infrastructures, as well as the continuing growth in remote work, online collaboration, and new service delivery practices such as telemedicine, will continue to drive dramatic growth in the semiconductor market and reshape the competitive landscape. Buckle your seatbelts!

Calibre Design Solutions was ready for DAC in-person and online, with a multitude of self-paced videos presenting details of the advances in functionality and performance introduced in the Calibre Design toolsuite over the past 12 months (oh, and a new product line!). If you weren’t able to make it to DAC 58, either in person or virtually, here’s a sampling:

Shift-left initiative

Design companies are always looking for ways to save time and solve design flow bottlenecks. The Calibre Design “shift-left” initiative focuses on making Calibre technology available earlier in the design process, enabling P&R and design teams to find and fix design issues faster and more easily, ultimately reducing the number of signoff iterations needed and speeding up time to market.

Enhanced P&R designer productivity and design quality

Jeff Wilson (Siemens EDA)

Three technology enhancements to reduce time to market and improve design quality:

- The Calibre ECO fill flow enables designers to adjust/insert fill around the areas of last-minute layout changes, reducing both timing impact and overall time to market.

- Improve reliability and reduce resistance by maximizing the automated insertion of DRC-clean vias.

- Insert DRC-clean filler, DACP, and ECO cells before physical verification, eliminating the “rip and replace” approach.

Calibre RealTime platform overview

Srinivas Velivala (Siemens EDA)

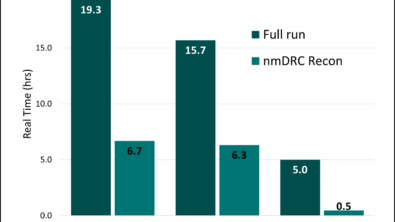

The Calibre RealTime platform brings interactive Calibre nmDRC checking into the custom and digital design environments. Designers get immediate Calibre nmDRC feedback, enabling them to reduce DRC iterations and runtimes.

Accelerate PV closure using Calibre RealTime Digital DRC

Srinivas Velivala (Siemens EDA), Shayan Mishra (Google)

Google shares their experience and results when using the Calibre RealTime Digital DRC solution in their design flows to accelerate DRC closure.

Calibre RealTime Digital in Aprisa

Swathi Rangarajan (Siemens EDA)

The Calibre RealTime Digital platform brings Calibre nmDRC into the Aprisa P&R environment, enabling digital designers to get DRC feedback on early-stage designs, accelerating the DRC closure process and shaving weeks off their tapeout schedule.

Accelerating your circuit verification cycle with Calibre nmLVS Recon

Carey Robertson, Kesmat Shahin, Anand Savadetti (Siemens EDA)

The Calibre nmLVS-Recon solution enables design and verification engineers to move through early-stage circuit verification more quickly and efficiently, leading to an overall reduction in delivery schedules and time to market.

Reliability verification

Complementing sign-off reliability foundry rule decks with designer-facing checks

Matthew Hogan, Hossam Sarhan (Siemens EDA)

New to formal reliability verification? Foundry-qualified reliability rule decks not only provide uniform baseline reliability criteria, but also the opportunity to replace time-consuming and resource-intensive proprietary solutions with foundry-maintained checks.

Parasitic extraction

Parasitic extraction throughout the design flow: From IP to sign-off

Carey Robertson, Aya Mohamed (Siemens EDA)

Using Calibre parasitic extraction tools throughout the design flow, including integration into different design platforms and downstream flows.

Cloud computing

Calibre cloud solutions: Samsung, Microsoft Azure

Michael White (Siemens EDA), Richard Paw (Microsoft), Giancarlo DiPasquale (Azure)

Physical verification compute requirements challenging your schedules? In collaboration with our strategic partners, Siemens demonstrates the successful use of key Calibre physical verification and DFM products with Samsung 7LP decks in the Azure cloud, providing the flexibility to leverage hardware resources in the cloud and accelerate design to market schedules.

Next-node productivity

Calibre physical verification – Solutions for your next node

Michael White, John Ferguson (Siemens EDA)

With the continuous growth in both rule requirements and layout database sizes and geometry counts, it is critical to ensure optimal performance and accuracy to meet yield and time to market requirements. At every node, the Calibre physical verification solution enables the fastest total turnaround times and reduced iterations for the largest, most complex designs covering the most complex checking needs.

Silicon photonics

Siemens EDA & Calibre solutions for silicon photonics

Michael White, Basma Serry (Siemens EDA)

Silicon photonics is an emerging market with the potential to produce unprecedented successes in many fields like telecommunications, data transfer, and medical devices. The Siemens silicon photonics design and verification platform enables design companies to reap the benefits of silicon photonics designs with Calibre confidence.

mPower

The mPower toolsuite, first introduced last September, provides innovative technology that enables fast, accurate, scalable power integrity analysis for both analog and digital designs, regardless of design complexity, size, or process node.

Dynamic EM/IR analysis on large analog circuits with mPower

Joe Davis (Siemens EDA), Kishore Kathula (MaxLinear)

Traditional EM/IR approaches can’t handle large analog designs consisting of millions of transistors. The mPower Analog high-capacity dynamic analysis technology enables designers to perform EM/IR analyses that were previously impossible.

Deploying mPower EM/IR for complex mixed-signal designs

Joe Davis (Siemens EDA), Khandaker Azad (ONSEMI)

ONSEMI uses the mPower Digital tool in their production sign-off flow perform accurate prediction of power, EM, and IR, and mPower Analog to complete EM/IR analysis on designs that existing tools couldn’t handle.

Quite a lineup, eh? We’ve also made all these videos available for viewing here.

Watched a video and have questions? Just contact your Calibre representative for more information. What, you don’t HAVE a Calibre representative? Send us an email, and we’ll get you connected!

Now, who’s ready for DAC 2022??!! Summer in the city…