The Grapes Are Back! And Cake! And C Tests with UVM and Transactions For All! Easy.

The grapes have returned – this weekend was “harvest” time. Jelly everywhere. A lot like this year here at Siemens. Lots of activity. New products. Announcements. Products everywhere. Jelly everywhere.

We’ve had a big year with our Questa One Launch, lots of things going on and lots of great new products.

But today is about going back to DVCON Japan 2024 and DVCON Japan 2025 (just completed). Before we get to “cake” and transactions and all the rest, don’t forget – DVCON Taiwan 2025 and DVCON India 2025 are both this week – hopefully if you’re in the area you’ll stop by and check-out all the new things at our booth – and maybe attend some presentations.

C Tests with UVM

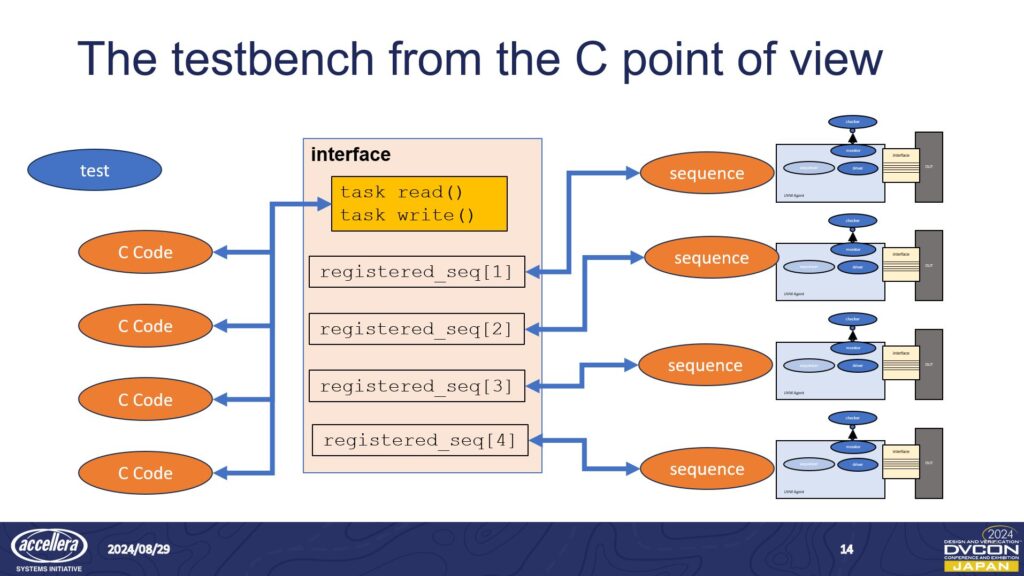

For me, DVCON Japan 2024, was about “Having Your Cake and Eating It Too – Programming UVM Sequences with C Code” with Tomoki Watanabe. It was a romp through connecting C code to UVM sequences using a mapping in an interface. Not as hard as it sounds, with some diagrams, explanations and example source code.

The idea being – have your cake and eat it too – have your standard UVM verification environment, and have your C verification environment connected. Have C tests running at the same time as UVM tests – sharing the same sequencer and driver.

Correlation with Transactions in the Wave Window

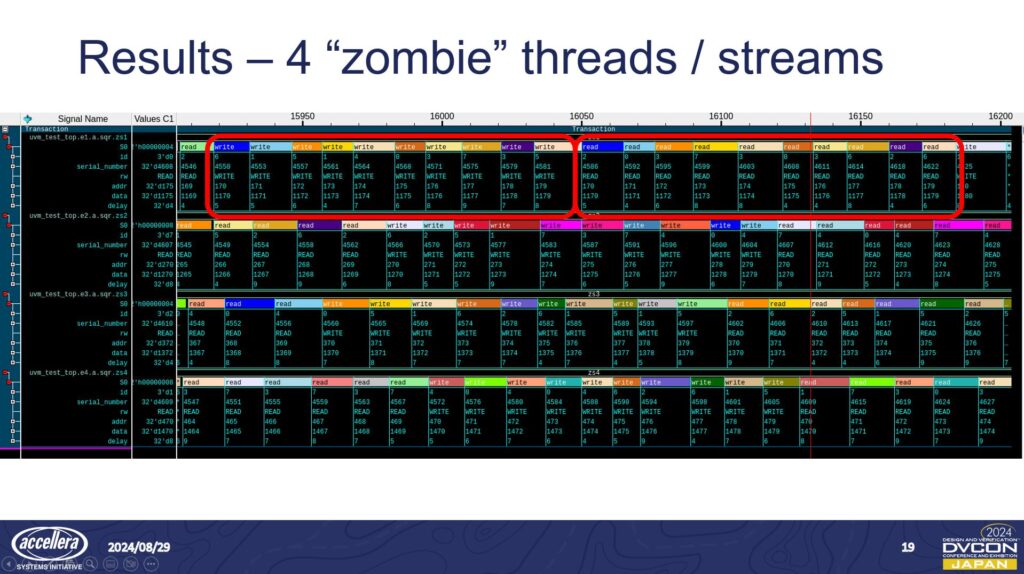

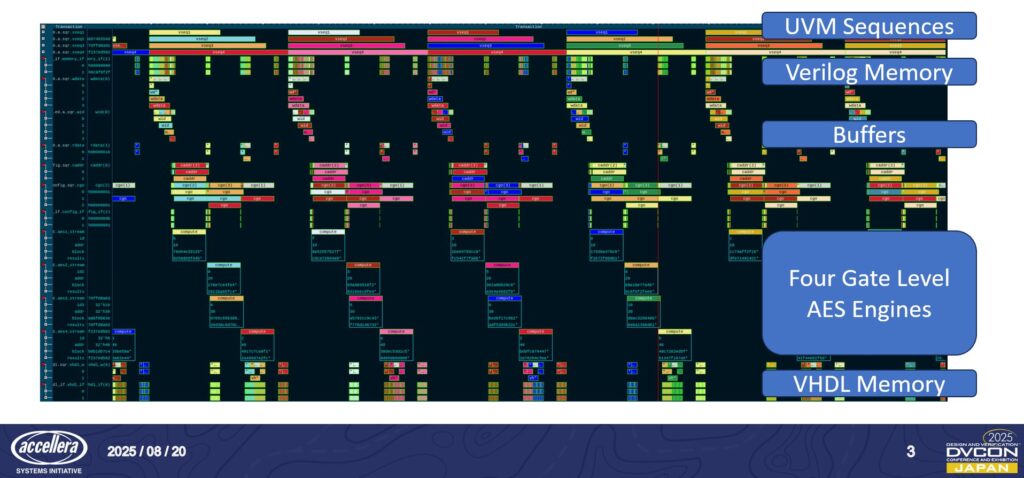

DVCON Japan 2025 was about “SystemVerilog Transactions, UVM and C – Correlation in a functional verification environment” – Correlation in the wave window using transactions.

In the paper with Tomoki Watanabe, we demonstrate how valuable correlated data is – and that the wave window is a great place to correlate things – by time. But the neatest part is that we correlated C code, UVM sequences and tests, VHDL, Memory reads and writes, Gate level designs using bind, and even backdoor access. The wave window correlation is with transactions – so most of the “places” above needed some transaction recording instrumentation. It’s real easy to do, and quite valuable for debug and verification.

I know that’s a lot. But the visibility is worth it. It was an exciting two years at DVCON worldwide and at Siemens EDA with our Questa One.

See you next time. Have fun verifying…

Links

Papers and Presentations can be found at

- DVCON Japan 2025 Paper / Presentation – “SystemVerilog Transactions, UVM and C – Correlation in a functional verification environment”

- DVCON Japan 2024 Paper / Presentation – “Having Your Cake and Eating It Too – Programming UVM Sequences with C Code”

- Classic Homemade Wild Grape Jelly Recipe