User2User 2024: Chiplets for future automotive application: Fraunhofer

In this User2User 2024 session entitled, Chiplets for future automotive application presented by Andy Heinig, Head of Department Efficient Electronics at Fraunhofer, explains why automotive is especially a good market and enabler for chiplets and presents different use cases for chiplets that are on the horizon.

Andy begins by describing three unique use cases for the data center, measurement equipment and automotive. He explains that although the data center is a good use model for the US, it is not for Europe; however, automotive is a main driver for chiplets and is a good fit for European companies due to the large number of automotive manufacturers as well as companies along the automotive supply chain. Andy rounds out his presentation by discussing trends, architectures and applications for chiplets in automotive, highlighting the need to explore hardware/software architectures and co-optimization for automotive applications.

Why chiplets make sense for automotive

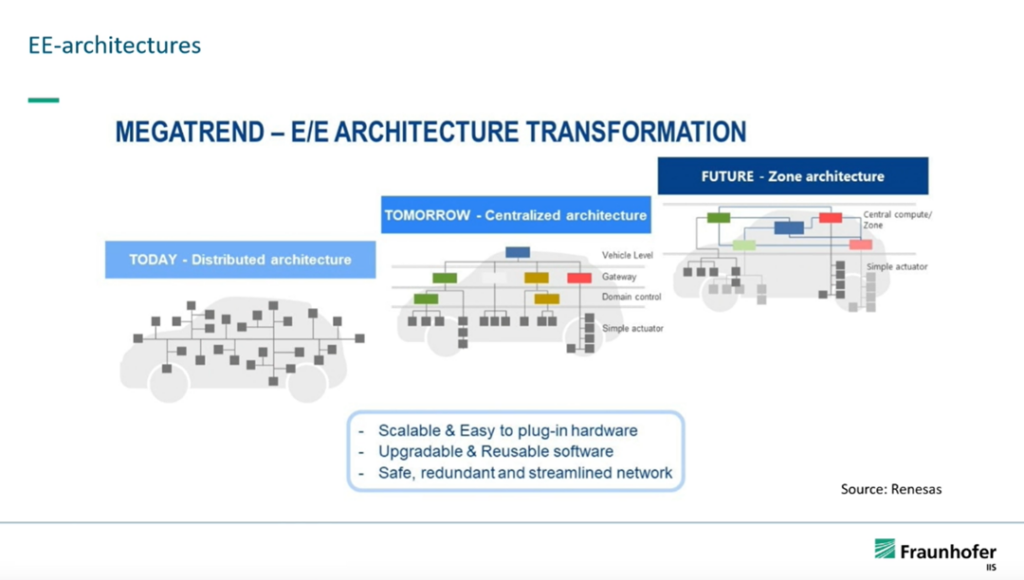

The automotive industry is transitioning to centralized “zone architectures” with 1-5 high-performance computing units. This centralization of compute power enables the adoption of advanced chiplet architectures in automotive applications.

Future automotive zone architectures feature a central high-performance computer (HPC) with digital processing and interfacing, using data center-like chiplets. Rear and front zones contain chiplets for analog-digital conversion and some compute, all connected via high-speed Ethernet.

What are the challenges for zone controllers and HPC?

Automotive HPC architectures require careful design to optimize data flow. Current designs route sensor data through a central hub multiple times, causing bottlenecks. More application-specific architectures, like connecting ADCs directly to eFPGAs before the hub, can improve efficiency but reduce flexibility for different algorithms.

The hub-centric approach offers flexibility but may not meet performance requirements due to excessive data traffic. Finding the right balance between efficiency and flexibility requires extensive hardware-software co-optimization. Andy points out that the industry is just beginning to explore these architectures.

What about test and reference systems for HPC chiplet architectures?

Fraunhofer is working with partners to develop reference systems for automotive HPC chiplet architectures. One such system uses a large amount of wire die-to-die interfaces (though UCIe is also being considered), PCIe Gen5 for sensor connectivity, and DDR5 for memory, all implemented in a 5nm Samsung process. The goal is to demonstrate interoperability between chiplets from different partners using a standardized interface.

However, challenges remain in bringing up these complex multi-chip, multi-core systems, particularly in distributing software and coordinating data transfer between chiplets. More standardization is needed to enable seamless software integration and “Lego-style” plug-and-play functionality for both hardware and software components.

To support the development of these systems, advanced tools are required, including system-level modeling languages, chiplet integration tools for 3D integration, and accurate electrical, thermal, and mechanical 3D solvers. Correlation between simulated and measured results is crucial to avoid costly and time-consuming re-spins due to first-time failures. A comprehensive toolset that bridges the gaps between chip, package, and PCB interactions is essential for designing complex automotive chiplets.

What chiplet technology variations are available from Fraunhofer?

Fraunhofer offers various chiplet integration technologies for automotive applications, each with its own advantages and disadvantages. Silicon interposers allow for HBM integration and advanced die-to-die interfaces but are expensive. Embedded bridges, manufactured in silicon or glass and integrated into a mold material, provide a balance between performance and cost, enabling HBM integration and larger panel-based processes. Organic interposers, using advanced materials with small line spaces, are more affordable but limited to older memory types like DDR, LPDDR, and GDDR.

The choice of technology depends on the specific requirements and cost constraints of the automotive application, with embedded bridges potentially suitable for high-end cars and organic interposers for mid-cost cars. System-level modeling is essential for exploring the optimal technology choice based on desired performance, features, and cost, allowing early collaboration between engineering and marketing teams to determine the most suitable solution.

Watch this informative User2User video recording, now available on demand, to learn more about how Fraunhofer is exploring and approaching hardware/software architectures and co-optimization for automotive applications.

If you missed User2User 2024 or attended the event and want to watch the 3D IC sessions again, the library of videos is now available on-demand here: Click here

To learn more about Siemens EDA 3D IC solutions, visit our 3D IC Homepage