Leveraging Reliability-Focused Foundry Rule Decks

By Matthew Hogan, Mentor Graphics

Using your foundry’s reliability rule deck early on lets you correct reliability issues while they cost less to fix.

Not that long ago, all designers had for integrated circuit (IC) reliability verification was a plethora of home-brewed scripts and utilities they combined with traditional design rule checking (DRC), layout vs. schematic (LVS) comparison, and electrical rule checking (ERC) tools. There were no foundry reliability rule decks or qualified reliability verification tools to provide a central focus on, or automated process for implementing reliability checks. While SPICE simulation is still widely used for small blocks, the ease with which reliability issues can be overlooked at the circuit level (particularly for electrical overstress) is staggering. Missing an input vector or running too few simulation cycles to expose an issue are some typical concerns (and weaknesses) of the SPICE methodology. On the interconnect side, traditional reliability verification means using your favorite parasitic extraction tool, selecting the paths you know/care about for export, and running SPICE on your parasitic netlist to determine resistance. Quite the laborious and error-prone undertaking. Understanding the circuit structure (topology), interconnect, and physical layout of your design are critical when looking at reliability-focused issues, especially those involving electrostatic discharge (ESD) and latch-up (LUP). Despite the challenges of these approaches, the question from designers always seemed to be “How can I leverage this technology if I don’t write the rules myself?”

Reliability-Focused Foundry Rule Decks

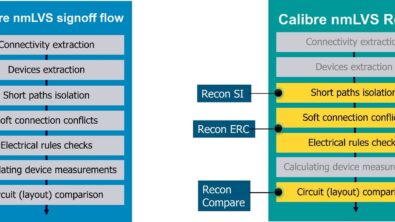

The fabless ecosystem relies on the availability of comprehensive, well-qualified foundry rule decks for a broad range of process nodes. Over the last decade, collaboration between electronic design automation (EDA) companies and the world’s leading foundries have resulted in the creation and availability of reliability-focused IC verification rule decks that consider design intent. While DRC, LVS and design for manufacturing (DFM) have been well-ingrained deliverables for this ecosystem for years, these new decks have enabled the development of qualified automated reliability verification solutions, like the Calibre® PERC™ reliability verification platform from Mentor Graphics [1], to help designers specifically address more complex reliability design issues accurately and efficiently.

Because new node development allows for the introduction of new tools and design flows, and creates the opportunity to solve new problems, many recent press releases focus on emerging node technologies [2][3][4][5][6]. However, while established nodes like 28 nm and 40 nm may not get much press these days, reliability rules are also available for them, focusing primarily on ESD and LUP.

Many designers are now beginning to understand the value of using these foundry reliability rule decks and automated reliability verification to augment their internal reliability checking flows for a wide variety of complex reliability issues.

Early and often

As with other verification solutions, getting insight into problematic areas of the design that affect reliability earlier in the design process is extremely beneficial, reducing the extensive re-work and re-spins that destroy schedules and eat into profits when errors are discovered late in the flow. For example, ensuring that the interconnect at the intellectual property (IP) level of your design is robust is a check that can be run early in the design process, as can cross-domain and similar topology-based checks. Many rule decks have options to facilitate running reliability checks not only at the full-chip level, but also at the IP level. Utilizing these capabilities in an incremental approach helps provide context for problematic areas, particularly for IPs that are being used in a different context from previous implementations, or whose geometries have been shrunk to accommodate a new process node.

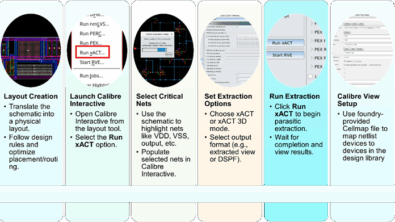

I often hear the statement that early reliability analysis cannot be done because the chip is not “LVS-clean.” False! While making sure you have no power or ground shorts when doing ESD or other power-related checks is critical, there are a whole slew of LVS errors that have no impact on ESD protection structures and evaluation. By understanding your design, and identifying the LVS errors that can impact the reliability verification results, you can achieve significant design closure benefits from employing early reliability verification. Of course, final sign-off verification can’t happen until your design is both DRC- and LVS-clean, ensuring accurate results, but the adoption of an “early and often” policy towards reliability verification will help you influence critical aspects of the design implementation while there are fewer barriers and lower cost to changes. Such checks as point-to-point (P2P) resistance, or current density (CD) issues due to inadequate metallization and/or insufficient vias, can be readily identified and rectified in the layout, as can topology issues for important protective structures like ESD or cross-domain circuits. Leveraging the foundry’s reliability checks with an automated reliability verification tool early in the design/verification cycle establishes an important baseline to identify potential issues without incurring significant costs in time and resources.

Conclusion

Foundry rule decks and qualified EDA tools have permitted the fabless ecosystem to flourish. Together, their trusted and well-qualified content and processes provide the foundation for your verification flows. With the proliferation of reliability-focused foundry rule decks, early verification of reliability issues and comprehensive full-chip runs can now leverage their guidance. As with more traditional DRC, LVS and DFM rule decks, augmenting your processes and flows with these foundry offerings and qualified tools provides you with the flexibility to implement reliability verification early in your design process, while ensuring confidence in the results.

References

[1] Fabless/Foundry Ecosystem Solutions, https://www.mentor.com/solutions/foundry/?cmpid=10167

[2] Mentor Graphics Enhances Support for TSMC 7nm Design Starts and 10nm Production https://www.mentor.com/company/news/mentor-tsmc-7nm-design-starts-10nm-production?cmpid=10167

[3] Mentor Graphics Announces Collaboration with GLOBALFOUNDRIES on Reference Flow and Process Design Kit for 22FDX Platform, https://www.mentor.com/company/news/mentor-collaboration-globalfoundries-22fdx-platform?cmpid=10167

[4] Intel Custom Foundry Expands Offering with Reliability Checking Using Calibre PERC, https://www.mentor.com/company/news/mentor-intel-custom-foundry-calibre-perc?cmpid=10167

[5] UMC Adds Calibre Reliability Verification and Interactive Custom Design Verification to Design Enablement Offering, https://www.mentor.com/company/news/mentor-umc-calibre-reliabillity-verification?cmpid=10167

[6] SMIC Adds Reliability Checks to IP Certification Program Based on Mentor Graphics Calibre PERC Platform, https://www.mentor.com/company/news/smic-to-ip-cert-program-mentor-calibre-perc-platform?cmpid=10167

Author

Matthew Hogan is a Product Marketing Manager for Calibre Design Solutions at Mentor Graphics.

Liked this article? Then try this –

White Paper: Improving Design Reliability by Avoiding Electrical Overstress

This article was originally published on www.semimd.com