2-5X Productivity Improvement in 14FDSOI Layout Design: STMicroelectronics Experience with Calibre RealTime

By Atul Bhargava and Mehak Malhotra, STMicroelectronics, India and Srinivas Velivala, Mentor Graphics

Rather than just fixing DRC errors as fast as you can, why not just eliminate them from your design?

INTRODUCTION

Design rule checking (DRC) is extremely complex at 28nm and below, and can be the critical path to timely tapeouts and high-quality designs. At STMicroelectronics, Calibre® RealTime provided a 2-5X productivity improvement when used to fix DRC errors on an actual 14nm product design. Not only did Calibre RealTime provide immediate DRC feedback, which enabled fast and flexible debugging, but it also helped designers understand the new 14nm DRC rules, both of which contributed to implementing the optimum resolution for each DRC violation. With Calibre RealTime, designers could concentrate on optimizing the design, rather than simply fixing DRC errors as rapidly as possible, improving the quality of the layout while maintaining or reducing tapeout schedules.

CHALLENGES OF DESIGN RULE CHECKING AT ADVANCED NODES

DRC challenges at smaller nodes are a double-edged sword—both the number and complexity of design rules are increasing, extending runtimes and tapeout schedules. The impact has been particularly difficult on custom and analog/mixed signal layout designers as they seek to understand the new and complex DRC issues encountered at 28nm and below, such as on-grid, pitch, and lithography checks, complex line-end rules, multi-dimensional rules, pattern matching, and multi- patterning decomposition, to name a few.

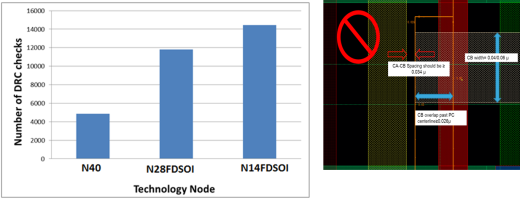

The 14nm node saw three times more checks than there were at 28nm, and many of these checks are complex and context-sensitive (Figure 1). At smaller dimensions, layout-dependent effects (LDEs) become more significant, and advanced techniques, like using local interconnect layers (LI) to achieve dense local routing before the first metal layer, introduce new DRC constraints. With this many new rules, coupled with the complexity of their implementation, designers can no longer rely solely on their memory to avoid creating design rule errors in layouts.

Figure 1: Custom designers can no longer rely on memorizing a limited set of design rules—there are simply too many, and they are too complicated.

Designers often find themselves fixing one DRC violation while creating another simultaneously, a fact that is not apparent until after the GDSII streamout and batch DRC run. So, if running physical verification outside the design environment is no longer optimum, what is the alternative?

CALIBRE REALTIME USE MODEL

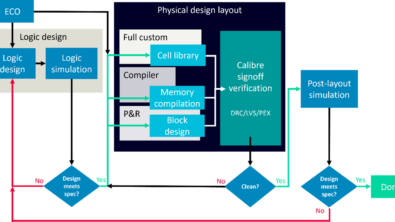

Calibre RealTime enables custom layout designers to access Calibre signoff DRC in the design flow, using full foundry-qualified Calibre rule decks and analysis engines (Figure 2). Tight interaction between Calibre RealTime and the design environment provides fast response times,

because streaming large GDSII files is not required. As designers create and edit the layout design, Calibre RealTime provides immediate signoff DRC feedback, enabling them to minimize design cycle time while creating improved layouts.

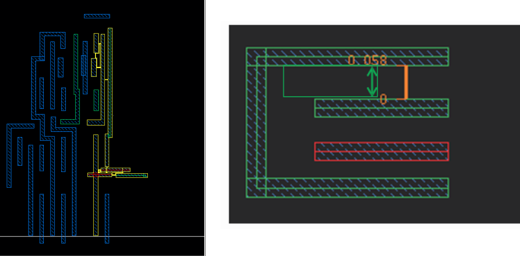

One important caveat—Calibre RealTime was designed for use on cell/block layout designs containing up to 3 million geometries, not an entire design. Above that number, efficiency declines, and the value of using Calibre RealTime in place of a batch DRC run diminishes. However, in larger designs, users simply zoom in to a part of the layout, and launch a Calibre RealTime run “on demand” within the layout editor (Figure 3). As designers make edits to the layout, they activate the “Run DRC in Window” function to start a Calibre DRC run. Calibre RealTime provides direct calls to Calibre analysis engines running foundry-qualified Calibre rule decks. These Calibre engines perform fast, incremental checking in the vicinity of shapes being edited, providing nearly instantaneous feedback on design rule violations, as well as systematic variation susceptibility (as measured by recommended rule compliance). Users can also create customized check recipes that will only generate violations for specific design rules of interest.

Figure 2: Calibre RealTime offers dynamic signoff-quality DRC to custom and analog/mixed-signal designers through the OpenAccess runtime model.

Figure 3: Calibre RealTime allows designers to perform DRC checks in specific areas of a design from within their design environment.

With its ability to perform all checks that can be run with Calibre DRC, including recommended rules, pattern matching, equation-based DRC, and multi- patterning, Calibre RealTime enables custom IC designers to correct and adjust their designs during the layout process to produce a design that is DRC-clean, resistant to manufacturing variability issues, and optimized for the most desirable performance and operational characteristics.

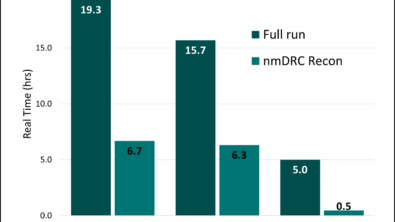

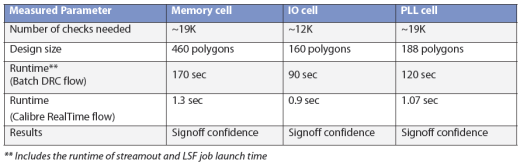

STMICROELECTRONICS’ EXPERIENCE WITH CALIBRE REALTIME

STMicroelectronics engineers used Calibre RealTime with a variety of design projects, including memory cells, IO cells, and PLL cells. They compared runtimes using a standard batch Calibre DRC run vs. Calibre RealTime running within the design environment. The results for a single iteration are shown in Table 1. However, memory design engineers typically run 20-25 DRC iterations a day, so the cumulative daily savings are substantially greater, giving the designers even more time to optimize the design for area and performance.

TABLE 1 – CALIBRE REALTIME RUNTIMES COMPARED TO TYPICAL BATCH RUNS DURING STMICROELECTRONICS 14FDSOI IP DEVELOPMENT

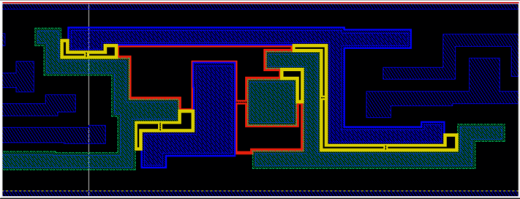

Multi-patterning rule checks that generate odd loop violations generally require “what if” analysis to evaluate multiple fix options and apply the optimal fix. Obviously, to attempt this with batch DRC requires multiple DRC runs. If cycle time is tight, designers may settle for a DRC-compliant, but less-than-optimal solution. Because Calibre RealTime provides instantaneous feedback, designers can evaluate each possible fix without sacrificing any quality enhancements (Figure 4). Additionally, because Calibre RealTime accesses full-featured Calibre analysis engines, designers can take advantage of the patent-pending warning rings in Calibre nmDRC™ to help them avoid propagating multi-patterning errors.

Figure 4: Using Calibre RealTime to try multiple fixes for double patterning violations helps designers quickly diagnose difficult odd cycle errors. Error warning rings also provide direct guidance on possible solutions.

CALIBRE REALTIME CHECK RECIPES

Calibre RealTime supports a verification technique known as check recipes, which allows STMicroelectronics designers to run only those checks they are interested in for a particular project task, rather than generating all DRC errors from the entire rule deck. This prevents unrelated error markers from overloading the layout design window. Without check recipes, designers can be distracted by seeing all the sign-off DRC errors that they are not interested in fixing at that particular moment. For example, the designers used check recipes to run specific 20nm checks, such as odd-loop checks and layout-dependent checks. The odd-loop recipe selected all the odd-loop checks by looking for the pattern “*odd cycle*” in the comments of the rule check.

Check recipes can also exclude certain checks. When working on a cell design layout, the designers used a check recipe to turn off the full-chip density and antenna checks generating DRC violations that are irrelevant until the cell is placed in the larger design. Another check recipe was created for the 28nm FDSOI process, containing all the checks run when using batch Calibre, minus any density checks (they were working on a small PLL design block and did not want to run density checks, which are more appropriate for large designs).

In short, check recipes help designers stay focused on the job at hand, and improve their productivity by eliminating irrelevant distractions.

COLLABORATION AND ENHANCEMENT

STMicroelectronics and Mentor Graphics collaborate closely to ensure that Calibre RealTime usage in the ST design flow is seamless. This cooperation also led to some Calibre RealTime enhancements that now benefit all users of the tool:

■ Load and use Calibre Interactive™ runsets within Calibre RealTime

■ Launch the customization GUI from the Calibre RealTime toolbar

■ Allow Calibre RealTime to read “cut size” via specifications

■ Identify the check-name of a DRC error by clicking on the error marker

CONCLUSIONS

STMicroelectronics found that Calibre RealTime makes signoff DRC a natural part of custom and analog/mixed signal layout design flow. Designers get immediate full DRC feedback as they edit their designs, and can configure specific check recipes that specify a subset of the complete DRC rules to focus the checking at different stages of the design process. Overall, STMicroelectronics determined that using Calibre RealTime provided them with a 2-5X productivity improvement when creating and verifying custom designs.