Siemens at DVCon U.S. 2026

Daily Summary of Siemens Events

Tuesday, March 3

- 12:00 PM to 1:00 PM. Siemens Luncheon Panel in Grand Ballroom AB

- 1:00 PM to 2:00 PM. Conference Keynote in Grand Ballroom CD

- 2:30 PM to 4:30 PM. Digital Twin Technical Lecture in Grand Ballroom D

Wednesday, March 4

- 10:00 AM to 12:00 PM. Formal Lecture on BMC acceleration in Magnolia

Thursday, March 5

- 9:00 AM to 10:30 AM. Agentic AI Tutorial. Grand Ballroom C

- 9:00 AM to 10:30 AM. CDC and RDC Standardization Part 1. Grand Ballroom D

- 11:00 AM to 12:30 PM. CDC and RDC Standardization Part 2. Grand Ballroom D

- 1:30 PM to 3:00 PM. HLS to Cloud FPGA Tutorial. Ballroom E

A Comprehensive Guide to Panels, Keynotes, Papers, Tutorials, and Workshops

DVCon U.S. returns to a larger venue at the Hyatt Regency Santa Clara. The expanded rooms and exhibit hall are intended to support a program heavily focused on AI in verification. Siemens EDA will have a significant presence throughout the week. This includes a sponsored luncheon panel, a major conference keynote, technical papers, and multiple tutorials that advance the state of verification, agentic AI, CDC and RDC standardization, and HLS to FPGA cloud prototyping.

Siemens Sponsored Luncheon Panel

From Engines to Intelligence. Managing Verification at Massive Scale

Type: Sponsored Luncheon Panel

Date and Time: Tuesday, March 3. 12:00 PM to 1:00 PM PST

Room: Grand Ballroom AB

Speakers: Harry Foster (Siemens), Darron May (Siemens), Vijay Chobisa (Siemens)

Abstract:

Verification complexity continues to grow as teams run more engines, larger regressions, and deeper analyses. Coordination across simulation, formal, emulation, prototyping, and growing pools of verification data has become a central challenge. This luncheon panel will highlight pragmatic strategies used by leading teams that combine commercial solutions with customized internal workflows. The discussion will also explore the evolution from raw engine throughput to intelligent, AI assisted analysis that helps teams prioritize risk and maintain confidence through scale.

Keynote Featuring Siemens Leadership

Beyond Bigger Designs. Rethinking Verification for the Era of Convergence

Type: Conference Keynote

Date and Time: Tuesday, March 3. 1:00 PM to 2:00 PM PST

Room: Grand Ballroom CD

Speakers: Abhi Kolpekwar (Siemens). Jean Marie Brunet (Siemens). Alon Shtepel (Micron)

Abstract:

Modern verification challenges are shaped less by design size and more by system level interactions. Hardware and software co behavior, power and performance states, and execution across multiple platforms create verification loops that cannot be solved with isolated tool optimizations. This keynote presents a combined architectural, hardware assisted, and practitioner focused perspective on how verification must evolve. AI and agentic workflows will become essential elements that support continuous, data driven verification.

Siemens Technical Papers and Lectures

- Enhancing Automotive ECU Design with Digital Twin Simulation

Comparative Study of Virtual Platform, FPGA Prototyping, and Edge Device Configurations

Type: Technical Lecture

Date and Time: Tuesday, March 3. 2:30 PM to 4:30 PM PST

Room: Grand Ballroom D

Authors: Sara Abd AlWahab (Siemens). Mohamed Abdelsalam (Siemens)

Abstract:

This presentation explores a unified digital twin methodology for automotive ECU development. The authors compare three execution environments. These include virtual platforms, FPGA prototyping systems, and the presentation also includes edge devices. The session will explain how each configuration impacts fidelity, software bring up, performance analysis, and system validation. The talk also highlights opportunities to reuse assets across the environments to improve coverage and reduce overall bring up time.

- Early Deep Bug Discovery via Rerun Acceleration and Parallel Multi Depth BMC Exploration

Type: Technical Lecture

Date and Time: Wednesday, March 4. 10:00 AM to 12:00 PM PST

Room: Magnolia

Authors: Sungjin Park (Siemens), Mark Eslinger (Siemens), and Samsung Electronics co-authors

Abstract:

This work introduces methods that accelerate deep bug discovery by combining rerun acceleration with multi depth bounded model checking. The approach allows multiple depth levels to be explored concurrently. This reduces formal convergence time and improves bug detection rates on complex SoC level verification problems.

- Optimizing Functional Fault Grading Flow for Memory Designs

Type: Technical Lecture

Date and Time: March 3. 9:00 AM to 10:30 AM PST

Authors: Euisang Yoon (Siemens), Arun Gogineni (Siemens), Sungyun Yoo (Siemens), Geonbeom Kwon (Siemens), Saurabh Srivastava (Siemens), and Samsung Electronics co-authors

Abstract:

As semiconductor technologies scale, random defect rates rise, increasing the need for effective post‑silicon memory screening. Structural test methods are common in logic devices but less viable for memories due to area cost, so functional test patterns remain essential. Fault injection simulation helps assess test coverage, but growing design complexity and expanding fault spaces make exhaustive simulation impractical. This paper introduces optimization techniques that improve fault injection efficiency, including static fault filtering, fault clustering, design pruning, stimulus grading, dynamic fault optimization, and parallel simulation management. Implemented in a commercial toolset and applied to a production NAND Flash design, these methods reduced total simulation time by more than 3x.

Tutorials and Workshops

- Agentic AI for RTL Signoff

Type: Tutorial and Sponsored Workshop

Date and Time: Thursday, March 5. 9:00 AM to 10:30 AM PST

Room: Grand Ballroom C

Presenters: Darron May (Siemens), Ronen Shoham (Siemens)

Abstract:

This session explains how agentic AI can transform RTL signoff by enabling automation that is context aware and workflow aware. The approach uses the Model Context Protocol. It enables design and verification tools to exchange semantic information in real time. AI agents can use this unified model to perform design space exploration. They can also perform targeted stimulus generation and automated debug. The session will show how these concepts reduce cycle time and improve signoff confidence.

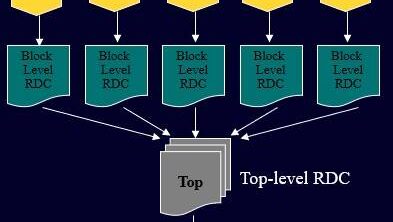

- Breakthrough in CDC RDC Verification. Defining a Standard for Interoperable Abstract Models

Part 1 and Part 2

Type: Sponsored Tutorial (Accellera)

Date and Time:

Part 1. Thursday, March 5. 9:00 AM to 10:30 AM PST

Part 2. Thursday, March 5. 11:00 AM to 12:30 PM PST

Abstract:

The Accellera CDC Working Group aims to define the first standard abstract model for CDC and RDC representations to ensure portability across tools and IP providers. The tutorial revisits CDC and RDC fundamentals. It outlines the reference verification flow. It then describes the draft specification that is intended to improve quality, remove vendor specific differences, and support modern SoC and chiplet based development. A status update on the LRM is included. The contribution from Siemens staff helped shape this content although onsite presentation will be given by another committee member.

- High Level Synthesis Meets FPGA Prototyping in the Cloud

Type: Sponsored Tutorial

Date and Time: Thursday, March 5. 1:30 PM to 3:00 PM PST\

Room: Ballroom E

Presenters: Sivasankar Palaniappan (Siemens), Mark Azadpour (AWS)

Abstract:

This tutorial demonstrates how HLS C++ testbenches can be reused when validating HLS generated RTL on Amazon AWS F2 FPGA instances. The flow maps the RTL to large multi-FPGA cards available in the cloud. The methodology allows teams to retain their high-level verification environment. This enables detailed RTL level validation without needing local FPGA infrastructure. The approach complements high level verification and provides scalability through cloud resources.

Siemens Exhibit Booth

The Siemens booth in the exhibit hall includes six dedicated demo stations. The Siemens presence at DVCon U.S. 2026 shows a clear theme as verification is shifting from tool centric workflows to interconnected, data driven, AI accelerated methodologies. Siemens contributions across panels, keynotes, technical papers, and tutorials reflect this direction. These sessions offer practical methods to manage complexity, improve analysis, drive interoperability, and accelerate signoff. To chat more with us about this, stop by our booth. See you in Santa Clara!