Getting Started with Questa Verification IP for Protocols

The best way to create a System on a Chip is with design IP: blocks that perform common functions such as interfaces to standard buses such as AMBA® AXI or PCIe. How do you then check that your chip works with the IP? You need to create stimulus that follows the protocol, but who has time to become an expert? The best way to verify your design is with Verification IP, or VIP.

Siemens Questa VIP (QVIP) is available for a wide range of protocols such as AXI, AHB, PCIe/NVMe, Ethernet, USB, Serial, plus DRAM and Flash memories. QVIP works with both SystemVerilog and VHDL designs, and easily integrates into a UVM testbench.

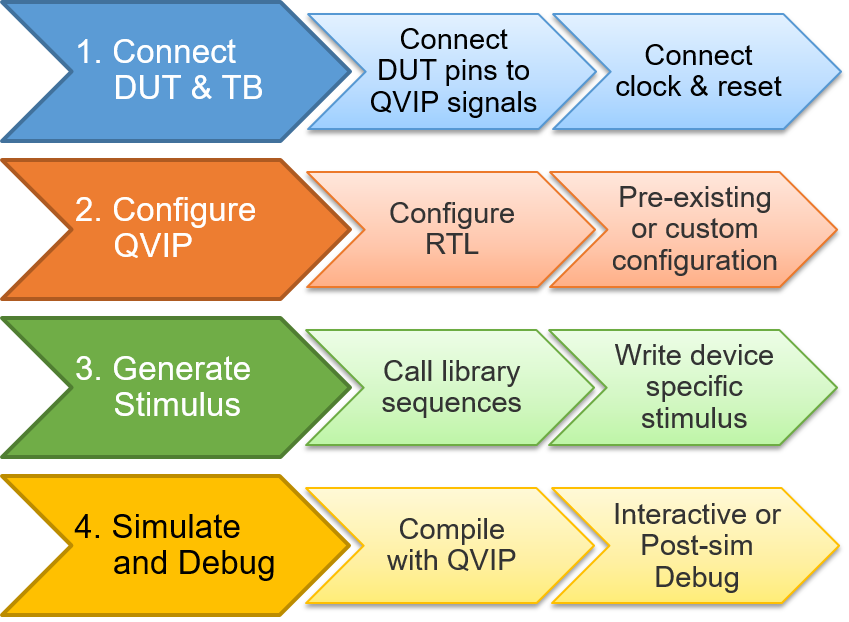

QVIP Integration Flow

Here are the four steps to connect QVIP to your testbench. The best part is that you can do the first three with the QVIP tool, Configurator, which also generates the files for the final step.

- Configurator reads your top netlist and creates a schematic symbol. You connect it to QVIP blocks such as an AXI master, plus clock and reset. The QVIP code, including the bus functional model and SystemVerilog Assertions are inside a single module, which reduces the number of connections.

- How wide are your RTL buses? How should the QVIP work with protocol features such as the RLAST signal in AXI? Specify these details in Configurator, either starting with a preexisting configuration or your own custom values.

- QVIP comes with a library of randomizable sequences for many protocols to get you started quickly, plus a generic read/write API to create stimulus specific to your design.

- Configurator generates a complete UVM testbench and netlist plus scripts, and support files for all major simulators. You can debug either interactively or after simulation completes. QVIP generates multiple log files so you can quickly see the high level transactions, and also the low level protocol-specific signals.

Diverse Verification Flows

Do you already have a UVM testbench, and want to add a QVIP agent? Do you want to see alternative topologies with masters, slaves, and monitors? QVIP comes with an extensive library of ready-to-run examples that you can explore.

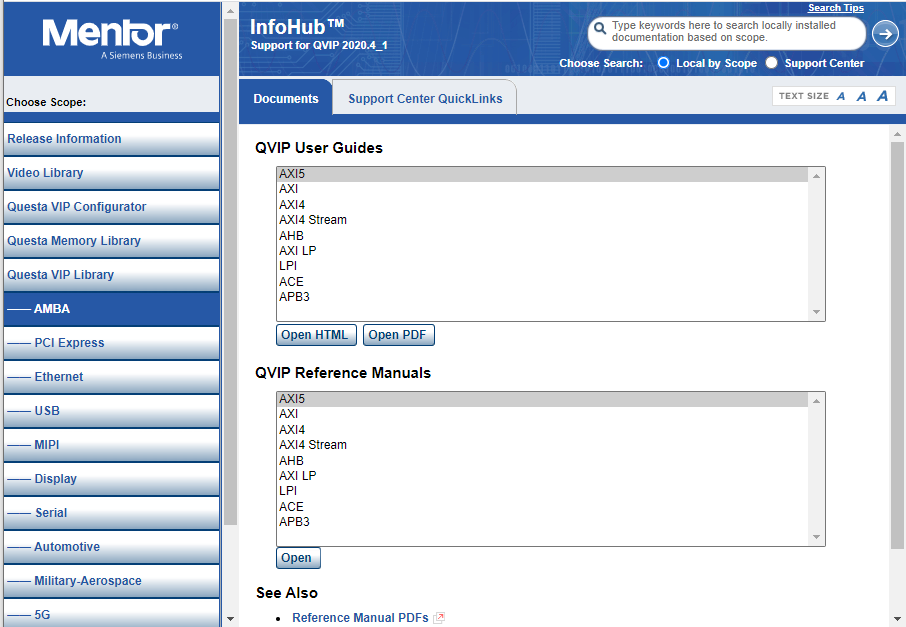

QVIP has User Guides for every protocol that walk you through the steps to verify your design. Need more details on a class, property, or method? The QVIP reference manuals have in-depth explanations of the QVIP bus functional model and SystemVerilog Assertions. There are even several video tutorials that walk you through popular topics such as injecting errors and debugging with Visualizer.

Training now available

Siemens has just released a 1-day QVIP class that covers all the above topics, and includes three labs so you can get hands-on experience with the tools. Learn more at