Shifting left with Calibre solutions: Enhancing IP design flow efficiency and design quality

By Terry Meeks

Designing integrated circuits (ICs) is a multifaceted task that requires the integration of various components, including intellectual property (IP). IP are reusable components that are integrated into larger IC designs. IP play a crucial role in IC design, enabling design companies to save time and resources by incorporating pre-designed functionality into their layouts. Although companies do develop their own proprietary IP, most IP is bought from specialty design companies. That makes it essential for IP to be ready for integration into any design style without creating implementation errors. It also means IP companies are always looking for ways to deliver IP to the market faster, while maintaining high quality and yield. Let’s delve into the world of IP design, exploring different types of IP, the IP design flow, and how early design stage verification can help IP designers meet their market goals.

IP design: A brief overview

IP includes designs such as analog-focused applications, digital logic blocks, memory blocks, and standard libraries consisting of logical gates and functions. IC design companies use IP to eliminate the need to recreate functionality for each new IC layout. Whether IP is acquired from specialized IP design companies or developed in-house, it requires specialized knowledge and experience to maximize its capabilities.

Types of IP designs

IP can be categorized into three main types: hard, soft, and custom.

1. Hard IP: Hard IP includes cores and standard cells that are custom-designed and certified by a foundry when a process technology is defined. It is typically subjected to rigorous verification, including design rule checking (DRC), layout vs. schematic (LVS) verification, and reliability/electrical rule checking (ERC). Hard IP is highly reliable and often sought after for critical components of IC designs.

2. Soft IP: Soft IP is generated by compiling SRAM from pre-defined cell libraries. Ensuring the integrity of SRAM-generated IP components is critical, as even subtle modifications during compilation can lead to performance or yield issues. Tools like the Calibre Pattern Matching tool help analyze IP layouts against foundry requirements, ensuring the reliability and performance of soft IP when compiled.

3. Custom IP: Custom IP is typically created for specific designs or to implement patented functionality. IP designers manually create IP layouts, running DRC, LVS, and reliability/ERC verification in a sequential process requiring multiple iterations throughout the design flow.

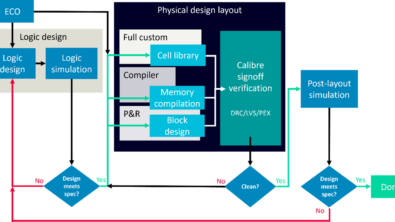

The IP design flow

The traditional IP design flow uses various electronic design automation (EDA) tools to create the logical circuit, implement it in a physical layout, and verify design manufacturability and performance against foundry design rules through DRC, LVS, and reliability/ERC. Engineering change orders (ECOs) can introduce design changes at any stage, necessitating further iterations. Once all requirements are met and verification is successful, the IP can be released for use.

Over 90% of IC companies use the Calibre nmPlatform for signoff verification. Using the toolsuite preferred by all major foundries ensures that designs delivered for manufacturing will deliver the performance, reliability, and yield required for market success. In that same vein, using the Calibre nmPlatform for IP verification allows IP companies to deliver IP that is ready for successful integration into a wide variety of design styles. And, because the Calibre nmPlatform is used by foundries for process node development, both IP and IC design companies who need to deliver leading-edge node designs to market can depend on its readiness for production use.

Shift left verification

Design-stage verification, also known as shift left verification, is an innovative strategy that aims to detect and fix design issues as early as possible in the design flow, reducing the need for corrections during signoff (when they become more time-consuming and complex). Calibre Shift Left solutions provide a set of tools and functionalities that enable IP designers to implement design-stage verification in their design and implementation flows. These tools rely on the same proven Calibre rule decks and processing engines used for Calibre signoff verification, providing designers with assurance that fixes are Calibre-correct and signoff-compliant.

Watch more about Calibre Shift Left strategy and its place in IC design here: Calibre physical verification: an ecosystem solution (siemens.com)

Shift left verification in IP design flows

Commercial IP companies, as well as IC and SoC designers, benefit from using a single foundry-trusted verification toolsuite like the Calibre nmPlatform throughout the design flow, which not only ensures consistency in verification tools and processes, regardless of when they are used, but also provides signoff-quality results at every stage.

Benefits of shift left verification for IP design types

Calibre Shift Left solutions offer specific verification benefits for each type of IP design:

1. Hard IP: Hard IP is usually certified by the foundries for a given process node, and updated as new process nodes are introduced. Early design-stage verification helps IP designers quickly verify modified components in updated IP, minimizing retesting while ensuring reliability. The ability to quickly produce updated designs that achieve high confidence scores is a key factor in market success.

2. Soft IP: For SRAM-based soft IP, the compiled IP must precisely match foundry requirements when integrated into a larger design. Early verification with tools like Calibre SRAM Checker and Calibre Pattern Matching helps ensure that IP designers can more quickly produce IP that compile correctly, enhancing their marketability.

3. Custom IP: Custom IP designers can leverage the Calibre RealTime Custom tool for near-instantaneous Calibre signoff-quality verification in their design environment. Immediate error feedback and correction guidance enhance productivity by reducing signoff iterations while ensuring design quality.

Conclusion

In the competitive world of semiconductor design, the efficient and high-quality creation of IP is essential for market success. Implementing design-stage verification with Calibre Shift Left solutions enables IP designers to streamline their workflows, identify and fix issues early, and ultimately reduce time to market while ensuring the highest level of design quality and performance. By embracing shift left verification, IP designers and design companies can gain a competitive edge and achieve their business and design goals more effectively.

Calibre Design Solutions continuously improves its engines to optimize runtimes and minimize resource usage. We also offer automation, integration, and debugging capabilities that simplify and speed up the design verification process. This combination of advanced tools and the Calibre Shift Left approach empowers IP designers to meet the demanding requirements of the semiconductor industry with Calibre confidence, delivering innovative and reliable IP designs to market faster and more efficiently than ever before.

Still interested and want to know more? We continue to explore this topic in our recent technical paper, A game-changer for IP designers: design-stage verification (siemens.com)