Optimal ESD protection with Calibre PERC and Solido Simulation Suite

By Neel Natekar

Integrated circuit (IC) reliability engineers face the dual challenge of ensuring robust electrostatic discharge (ESD) protection without overdesigning protection circuits. Overdesigning not only increases chip area but also degrades the performance of high-speed and radio frequency (RF) circuits. Siemens EDA offers a novel solution that combines Calibre PERC reliability verification with the AI-accelerated Solido Simulation Suite, delivering context-aware SPICE simulation to optimize ESD protection. This blog explores how this innovative approach can help engineers strike the perfect balance between protection and performance.

Understanding the challenge: ESD protection in IC design

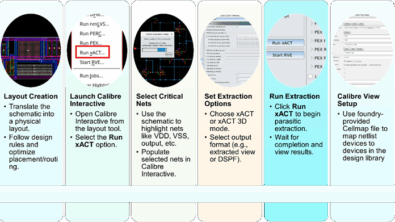

ESD poses a significant threat to the reliability of modern ICs, especially as design features shrink, and overall design complexity increases. Choosing optimal ESD design strategy is paramount for IC designers aiming to meet aggressive power performance and area (PPA) targets without compromising reliability. To do so, designers must understand the exact ESD design margin available and avoid under designing or over designing ESD protection circuits. The traditional approaches for ESD design and verification are simply inadequate when it comes to providing this information to IC designers. These methods require either manually partitioning the design or running ESD simulations at IP or small block level while estimating the interconnect parasitics from the higher levels of hierarchy and subsequently stitching them to the devices to model the distributed power ground network (figure 1).

Traditional ESD verification approaches are cumbersome and often lead to overdesign, as engineers err on the side of caution to prevent potential failures. They can expose users to the risk of manual errors and cannot be trusted for signoff.

The limitations of static ESD checking

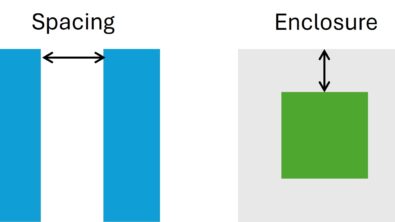

Static ESD checking is a well-established method that uses point-to-point (P2P) resistance rules set by foundries to ensure that ESD protection structures are effective. However, this approach has limitations, particularly when dealing with complex designs that involve distributed ESD protection schemes. Static checks may fail to capture the correct triggering of dynamic ESD protection circuits, leading to either unnecessary design modifications or missed potential failures.

Introducing context-aware ESD verification

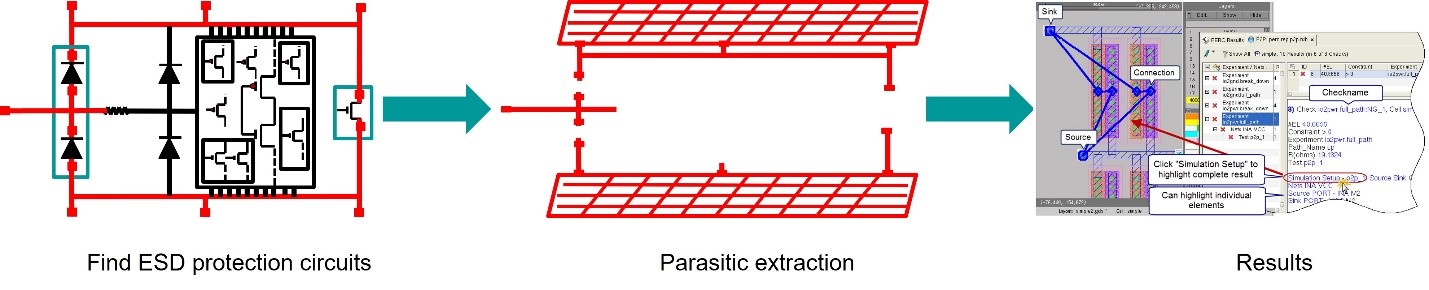

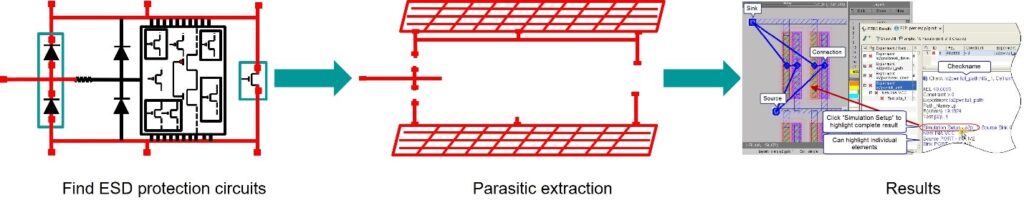

To address these challenges, Siemens EDA has introduced a context-aware ESD verification flow that combines the strengths of Calibre PERC and the Solido Simulation Suite. This innovative solution leverages the intelligence of Calibre PERC to identify and retain only the relevant portions of the design for ESD simulation. The simulatable netlist generated by Calibre PERC is then fed into the Solido Simulation Suite, enabling high-fidelity SPICE simulations that accurately capture the behavior of ESD protection circuits under real-world conditions.

Our powerful solution lets designers run full-chip ESD verification with high fidelity in a fully automated flow. With Calibre PERC + Solido, designers can determine the exact design margins, while also pinpointing where and when any devices exceed their breakdown limits, without the need for any manual hacking or approximations. This solution provides up to 8X performance gain over conventional simulation techniques without compromising on accuracy of results.

Use case 1: Verifying ESD discharge paths

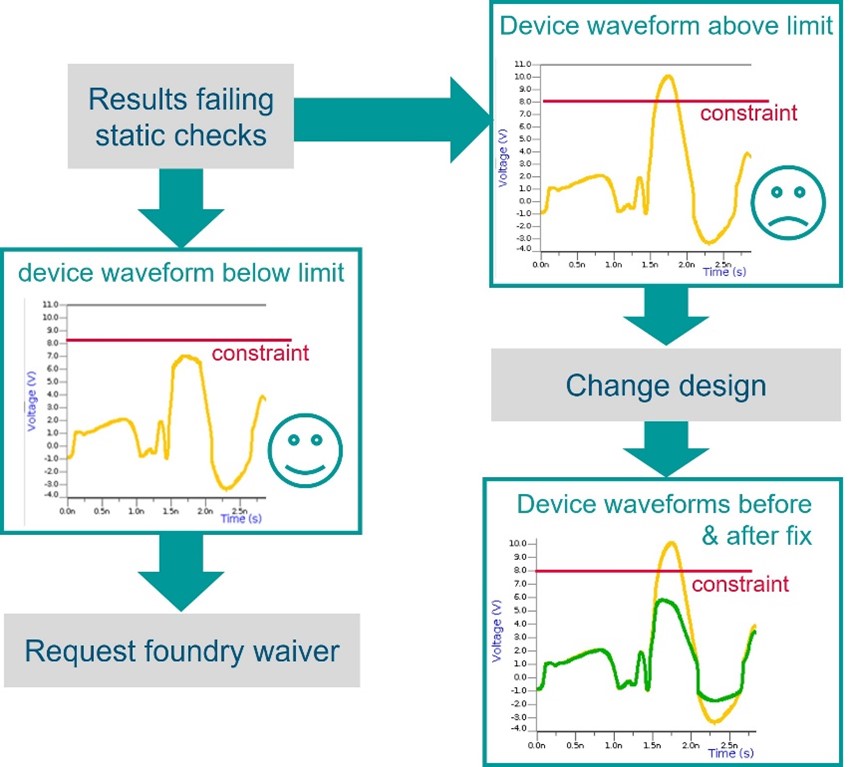

One of the key use cases for this technology is verifying whether devices are at risk of breakdown during an ESD event if certain discharge paths do not meet the foundry-specified resistance criteria. The context-aware flow automatically identifies failing paths and launches simulations to determine if these paths pose a risk to the devices. Engineers can then decide whether to request waivers from the foundry or make necessary design adjustments based on the simulation results (figure 2).

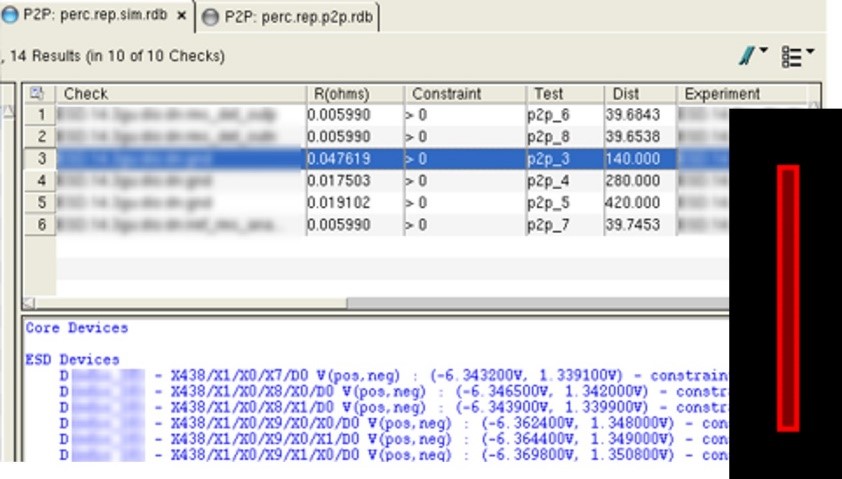

Use case 2: Evaluating ESD design margins

Another powerful application of the context-aware ESD flow is evaluating the design margins for ESD protection circuits. Engineers can specify top-level IO pins of interest, and the software will automatically simulate the relevant paths. The detailed reports generated from these simulations provide valuable insights into the exact voltages and currents experienced by the devices, allowing for more informed decisions about trimming or optimizing ESD protection in targeted areas of the chip.

The benefits of context-aware SPICE simulation

By integrating Calibre PERC with the Solido Simulation Suite, Siemens EDA has created a revolutionary approach to ESD verification that offers several key benefits:

- High-fidelity analysis: The context-aware SPICE flow provides accurate simulations that capture the dynamic behavior of ESD protection circuits, reducing the risk of overdesign and ensuring optimal protection.

- Automated, error-free process: The end-to-end automation of the flow eliminates manual intervention, reducing the potential for human error and ensuring deterministic results.

- Enhanced productivity: By focusing simulations on the most critical paths, engineers can achieve faster turnaround times and increase overall productivity.

Conclusion

As IC designs become more complex and performance-driven, traditional ESD verification approaches may no longer be sufficient. The context-aware SPICE simulation flow from Siemens EDA offers a powerful solution that combines precision with efficiency, helping engineers optimize their ESD protection designs while maintaining high performance. To learn more about how this technology can enhance your ESD verification process, download our full paper, Design optimal ESD protection using context-aware SPICE simulation