Safeguarding IC reliability: Calibre PERC’s latch-up guard ring check

By Mark Tawfik

“Reliability is not an act, it is a habit.” – Aristotle

This quote from the ancient Greek philosopher Aristotle underscores the importance of proactive and consistent measures to ensure the reliability of integrated circuits (ICs). In the fast-paced world of semiconductor design, where even minor glitches can lead to catastrophic failures, developing a reliable “habit” is crucial for staying ahead of the competition and delivering high-quality products to the market.

The costly threat of ESD and latch-up

Electrostatic discharge (ESD) events are estimated to cost the semiconductor industry a staggering $8 billion annually in lost productivity, warranty claims, and product failures, according to a 2018 Semico Insights report. Even the most seemingly innocuous static shocks can inflict critical damage on highly sensitive IC components, leading to immediate catastrophic failure, latent performance degradation, or parametric shifts.

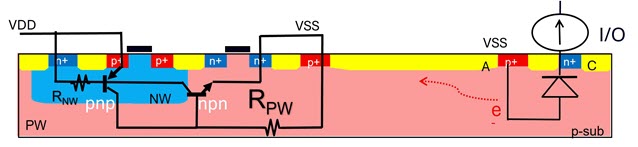

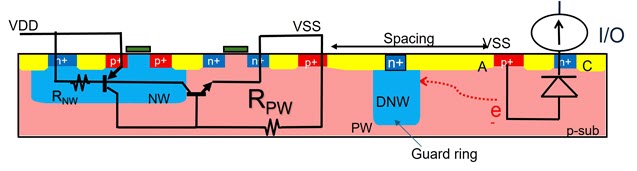

Complementing ESD as a paramount reliability concern is the insidious challenge of latch-up—the inadvertent triggering of a parasitic Silicon Controlled Rectifier (SCR) structure within the CMOS process. Once activated, this parasitic SCR can sustain a large, uncontrolled current flow, causing complete functional failure, thermal runaway, and even physical damage to the device. Latch-up events can be triggered by a variety of factors, including voltage transients, overvoltage conditions, or even an ESD incident that injects sufficient current. Figure 1 illustrates the components of a latch-up event.

Enhancing signal integrity and isolation with guard rings

Safeguarding ICs against these reliability threats requires a multifaceted approach, with the careful optimization of the circuit layout playing a crucial role. At the heart of this strategy are guard rings— heavily doped regions strategically placed around sensitive transistors and circuit blocks. These guard rings serve two key functions:

- They absorb minority carriers, preventing them from reaching and activating the parasitic bipolar transistors that constitute the latch-up path.

- They act as physical barriers, diverting excess current away from vulnerable areas and providing electrical isolation between different regions of the IC.

By minimizing unwanted interactions and maintaining signal integrity, guard rings help enhance the overall robustness and reliability of the integrated circuit. Figure 2 illustrates the location of a guard ring.

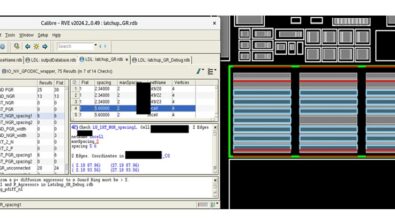

Calibre PERC’s robust latch-up verification checks

To ensure the effective implementation of these critical guard ring structures, the ESD Association (ESDA) has developed a comprehensive set of design rules and compliance checks. Building upon these industry standards, the Calibre PERC reliability platform from Siemens Digital Industries Software offers a suite of easy-to-use, pre-coded packaged checks that address various aspects of latch-up prevention, including:

- Verifying the existence of guard rings

- Checking the width of guard rings

- Monitoring the spacing between guard rings and aggressors

- Identifying potential victims in high-risk “danger zones”

- Confirming the connectivity of guard rings to the designated bias

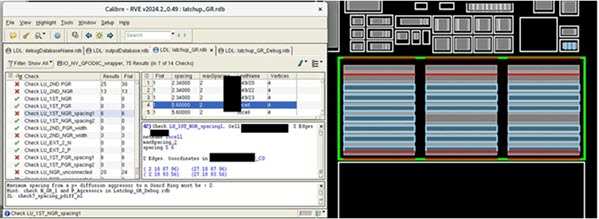

By enabling the early identification and resolution of latch-up issues during the design phase, these advanced Calibre PERC checks help designers significantly reduce time-to-market while improving yield, reliability, and compliance. Figure 3 shows visualization of PERC packaged checks in Calibre RVE.

For more information about the latch-up checks, download our technical paper Ensuring latch-up guard rings ESDA rules using Calibre PERC.

Streamlining reliability verification with packaged checks

While the ESDA’s guidelines provide a robust framework for latch-up prevention, the mere availability of these checks is only the initial step. Designers often face challenges in effectively setting up and executing the checks within their specific design environments.

To simplify this process, Siemens EDA has encapsulated the ESDA checks into pre-coded, packaged solutions that can be seamlessly integrated into a design team’s existing reliability verification flow. This approach eliminates the need for manually coding the checks and the associated complexities, allowing designers to focus on their core tasks while ensuring comprehensive coverage of critical reliability aspects.

Conclusion: Enhancing IC reliability and time-to-market

By leveraging Calibre PERC’s latch-up guard ring checks, IC designers can achieve rapid and precise reliability verification, thereby significantly reducing time-to-market. This innovative solution offers a user-friendly and efficient method to apply ESDA guidelines swiftly and accurately, enabling comprehensive latch-up protection across any technology node.

As Aristotle wisely observed, true reliability is not a one-time act, but a consistent habit. With Calibre PERC’s robust verification capabilities, designers can cultivate this habit, safeguarding the reliability and performance of their integrated circuits and staying ahead in the competitive semiconductor landscape.

For details, download our technical paper Ensuring latch-up guard rings ESDA rules using Calibre PERC.