Introducing Calibre DesignEnhancer design-stage layout optimization!

By Jeff Wilson

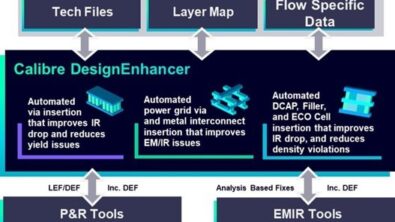

Introduced in early 2023, the Calibre DesignEnhancer tool is part of a growing suite of shift-left tools within the Calibre nmPlatform, aimed at facilitating earlier design optimization. The primary goal is to help design teams achieve their power, performance, and area (PPA) goals more quickly, with the confidence that comes from using proven Calibre technology.

The Calibre DesignEnhancer tool

The Calibre DesignEnhancer tool provides place and route (P&R) and custom/analog design teams with a fast and integrated environment for making multiple Calibre-clean design modifications that reduce voltage (IR) drop) and electromigration (EM) issues to improve design reliability, as well as optimize layouts for manufacturing. Ultimately, applying these modifications earlier in the design flow helps reduce late-stage iterations, shortening time to market.

Calibre DesignEnhancer use models address design challenges

Via insertion for reduced IR drop

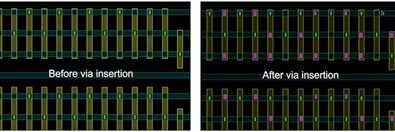

The Calibre DesignEnhancer Via use model focuses on reducing IR drop on user-specified nets. Leveraging detailed knowledge of design rules and connectivity, this feature maximizes the insertion rate of DRC-clean vias. It can be employed by both intellectual property (IP) and system-on-chip (SoC) designers, offering versatility in effectively addressing IR drop concerns.

A Via kit utility ensures quick, automated adaptations for different process technology nodes. For more detailed information, read our technical paper: Calibre DesignEnhancer Via kit utility ensures fast, accurate updates

Parallel run lengths insertion for power grid optimization

To combat IR drop issues on power grid structures, the Calibre DesignEnhancer tool power grid enhancement (Pge) use model inserts metal interconnect and vias in available white spaces or open tracks to create parallel paths. These modifications effectively reduce resistance on power grid structures, enhancing the overall performance and reliability of the design. Designers have the flexibility to target specific layout areas for insertions, ensuring maximum reduction in IR drop where it is most critical, while minimizing the impact on timing.

Filler/DCAP cell insertion for physical verification readiness

The Calibre DesignEnhancer physical verification readiness (Pvr) use model streamlines the insertion of decoupling capacitors (DCAPs), engineering change order (ECO) DCAPs, and filler cells in the P&R layout at the following stages: during floorplanning, after placement and after routing. Compared to P&R tool flows, this approach not only significantly accelerates the design readiness for physical verification with extremely fast runtimes, but because the Calibre DesignEnhancer tool relies on proven Calibre engines, all insertions are correct by construction and DRC-clean. Designers can also establish density targets for the insertion of DCAP and ECO DCAP cells, enabling precise control over their location and quantity in the layout and ensuring electrically-correct layouts. This fine-tuned approach allows teams to effectively address dynamic IR drop concerns.

Real-world applications and success stories

At DAC 2023, we had the privilege of introducing the Calibre DesignEnhancer tool and its functionalities. Speakers from industry leaders such as Juniper Networks and Intel shared their impressive results achieved by utilizing the Calibre DesignEnhancer use models on their production designs. These success stories underscore the tool’s effectiveness in real-world applications. See for yourself! Watch a video of that conversation: Calibre DesignEnhancer design-stage layout optimization for EMIR

While at DAC, we also had the opportunity to visit the Samsung booth and highlight the collaboration between Siemens EDA and Samsung. Together, they developed solutions based on Calibre DesignEnhancer use models, demonstrating the tool’s broad industry adoption and its potential to revolutionize design workflows.

Conclusion

The Calibre DesignEnhancer tool represents a significant leap forward in design physical verification and optimization. With its three versatile use models, it empowers design teams to tackle IR drop and EM issues earlier in the design flow with Calibre confidence in the results. Real-world success stories from leading companies underscore the tool’s effectiveness and its potential to drive innovation across the industry.

For additional information and resources, visit the Calibre DesignEnhancer product page on the Siemens EDA website.

Updated November 15, 2023