LVS Zero to Hero in 3 Easy Steps

By James Paris

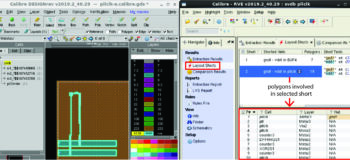

When it comes to system-on-chip (SoC) physical verification turnaround-time, layout vs. schematic (LVS) verification can make or break tapeout plans. Working through a rat’s nest of shorts often seems like an incomprehensible collection of polygons to the uninitiated. Many a designer has likely found themselves confronted with just such an issue late one night, when meeting the tapeout schedule hung in the balance. It’s times like these that an LVS hero is needed to save the day (and the schedule)!

Unfortunately, LVS debug hero status is not something you can acquire from being bitten by a radioactive spider or exposed to gamma rays. Instead, expertise is acquired over the course of multiple iterations across many different designs. Mastery requires familiarity with many different elements of LVS, including short isolation, HCELL configuration, when to use a black box approach, device-level circuit debug, and more. Is being bitten by a radioactive spider sounding easier? Hold on! There is a way to put yourself well on the LVS Hero path without such drastic measures.

First, start your journey by reading a few technical papers:

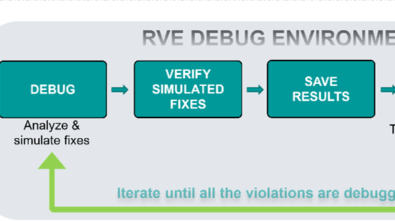

- Improving productivity with more efficient LVS Debug. This short introductory paper identifies the villains, um, challenges you’ll encounter during LVS debug, and how you can defeat them using the Calibre® RVE interface. Mastering these techniques are critical to a strong LVS debug foundation.

- Accelerate time to market with Calibre nmLVS Recon technology, a new paradigm for circuit verification. The innovative Calibre nmLVS-Recon™ tool lets you rapidly examine dirty and immature designs to find and fix high-impact circuit errors earlier and faster, leading to an overall reduction in tapeout schedules and time to market. It’s like a time machine for IC designs!

- Increase LVS verification productivity in early design cycles. Learn how to run targeted short isolation analysis and debugging on blocks, macros, and chips in early design phases with the Calibre nmLVS-Recon early verification tool, focusing on efficient, prioritized short isolation and short paths debugging that’s faster than a speeding train!

Second, expand your understanding of the short isolation process, learn about LVS black box flows, and explore advanced LVS topics through this collection of ten training videos. In these videos, our experts demonstrate exactly how to isolate shorts, explain how to use LVS Black Box, and perform advanced debug using the Calibre Query Server tool.

Third, take on a sidekick to help with the particularly challenging issues. Heroes don’t always go it alone, after all! Sometimes things don’t go according to plan, and you find yourself needing backup. No need for a bat signal, though—just reach out to one of our friendly Calibre LVS support team! This team has the full superpowers of the Calibre product team behind them to tackle any LVS issues that are beyond your current level of proficiency.

Achieving LVS Hero status can certainly help to limit late night debug sessions, and make you a highly valued resource superhero on any IC design team.