DFT Verification: Tackling the evolving challenges

Technological advancement continues as a blistering pace, and the demand for highly reliable systems is paramount across various industries. Safety critical systems and high-performance and heterogenous compute are just a sampling of end markets where customers require the utmost reliability.

Three significant megatrends are currently shaping the landscape in Design For Test (DFT).

Technology Scaling represents the implementation of new DFT architectures to maintain yields and margins at leading technology nodes.

Design Scaling encapsulates the hierarchical DFT methodologies required to deliver reliable products across highly complex architectures (System-on-chip, 3DIC, etc…)

System Scaling encompasses test technologies ensuring extra-high reliability throughout the silicon lifecycle.

Tessent Silicon Lifecycle Solutions is the industry leader providing cost-effective and scalable test solutions addressing the primary care-abouts: time-on-tester, high defect coverage, reduced test power, and more. In simple terms, tackling the big elephant in the room.

But we must not ignore the baby elephant; the rapidly evolving and growing challenge performing DFT verification.

Evolving DFT Verification Paradigm

The growth in verification effort and volume is a result of addressing the three industry megatrends.

At the technology scaling level, there is a rising per block cost to comprehensively verify across a growing number of corners and fault models. Beyond pattern verification across the various configurations, project teams must also verify the DFT infrastructure supplying patterns to the chains. It’s not uncommon to have 1000’s of different pattern sets, some executed in parallel, others in serial, to exhaustively test a single core.

The verification effort is magnified as designs scale with complex hierarchical DFT implementations containing multiple DFT cores. The impact is NxY verification cycles where N represents the number simulations/core and Y the number of unique cores in the the chip. Additionally, top level parallel and serial simulations are required after block level patterns are retargeted to the top level context.

Lastly, at the system scaling level, industry is demanding extra-high reliability from product introduction to decommission in an increasing number of markets. To meet this demand, companies are utilizing the additional coverage obtained from functional patterns as well as implementing in-system test capabilities (HW and SW) to execute patterns in-field and to identify and even predict when silicon will degrade to failure.

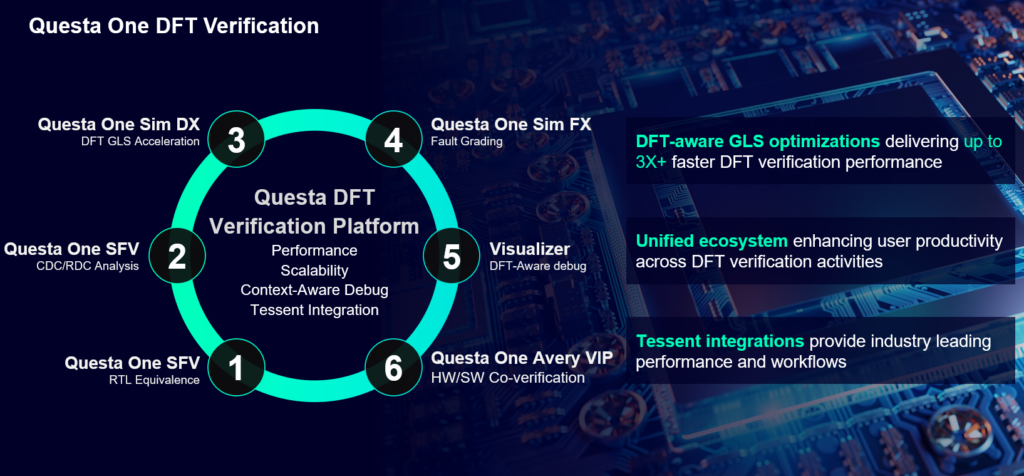

To combat the growing simulation runtime and sheer volume of verification cycles required, Siemens recently announced the Questa One DFT Verification solution. Within this solution exists a suite of technologies and workflows tailored to Tessent solutions, delivering an optimal user experience and an evolution in engine performance.

Questa One DFT Verification Solution

Through seamless integrations with Tessent Silicon Lifecycle solutions, the Questa One DFT Verification solution offers a unified platform that seamlessly connects verification into the entire DFT process. This integration enables efficient collaboration and streamlines the verification workflows, ensuring a holistic approach to DFT verification.

The Questa One DFT Verification solution consists of static/formal, simulation, and verification IP solutions. Capabilities include:

- Static analysis capabilities: pre- to post- RTL equivalence checking

- Automated directives for seamless CDC/RDC analysis after MBIST insertion

- Automated protocol SystemVerilog Assertion (SVA) generation for glitch scenario analysis

- Orders of magnitude advantage in gate-level simulation performance over existing solutions

- Scalable functional fault grading of functional patterns to increase test coverage

- DFT-aware debug and X-propagation analysis

- Software-aware verification IP for accelerated IST HW/SW co-verification

Customers are experiencing significant value with Questa One DFT verification solution, as highlighted by Microsoft during the recent Questa One launch.

“Questa One DFT (QDX) simulation utilizes advanced DFT-centric simulation capabilities to deliver faster performance than existing simulation solutions, slashing our verification time from weeks to days,” said Selim Bilgin, corporate vice president, Silicon Engineering at Microsoft. “In addition to these impressive speed ups, on Microsoft’s Azure Cobalt 100 platform, QDX delivers up to 20 percent further performance jump unlocking even greater efficiency for our EDA workloads.”

Want to learn more?

Dive deeper into the Questa One DFT verification solution at Verification Academy. Within, you’ll find white papers, videos, and additional resources to assist in evolving your DFT Verification methodology, taking advantage of the unique capabilities of Questa One.

Conclusion

As the semiconductor industry advances towards increasingly complex devices, ensuring the cost-effective and reliable delivery of silicon becomes a top priority. The Questa One DFT Verification solution delivers a comprehensive, scalable verification solution that integrates seamlessly with Tessent Silicon Lifecycle solutions, which stand at the forefront of innovation in addressing technology, design, and system scaling challenges.

The Questa One DFT Verification solution serves as a catalyst for faster DFT sign-off and reduced time-to-market and shapes the future of DFT verification. DFT-aware static analysis, formal analysis, logic simulation, fault simulation, verification IP, and advanced debuggers effectively equip project teams to overcome the DFT verification challenges of today and tomorrow.