Part 7: The 2022 Wilson Research Group Functional Verification Study

IC/ASIC Design Trends

This blog is a continuation of a series of blogs related to the 2022 Wilson Research Group Functional Verification Study. In my previous blog, I focused on FPGA design and verification trends. Now my plan is to shift the focus in this series of blogs from FPGA trends to IC/ASIC trends. And specifically in this blog, I present trends related to various aspects of design to illustrate growing design complexity.

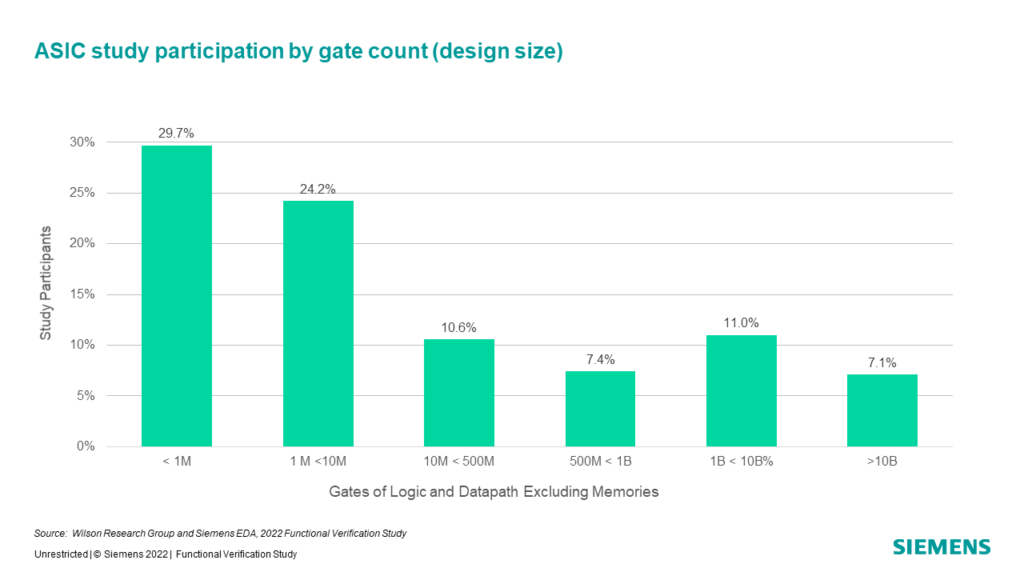

IC/ASIC Design Size by Gate Count

Fig. 7-1 shows the trends from the 2012 through the 2022 studies in terms of active IC/ASIC design project by design sizes (gates of logic and datapath, excluding memories). Keep in mind that Fig. 7-1 does not represent silicon volume (i.e., it represents study project participants).

One interesting observation from the past few study is the continue increase in design projects working on designs less than 1M gates. This is due to a number of projects working on smaller sensor chips for IoT and automotive devices. This can potentially yield some interesting results in the study.

A key takeaway from Fig. 7-1 is that the electronic industry continues to move to larger designs. In fact, about 36 percent of today’s design projects are working on designs over 10M gates, while 30 percent of today’s design projects are working on designs between 1M gates and 80M gates.

But increased design size is only one dimension of the growing complexity challenge. One industry driver that has had a substantial impact on IC/ASIC design and verification complexity is the emergence of new layers of design requirements (beyond basic functionality), which did not exist years ago, for example, security requirements, safety requirements, and requirements associated with hardware-software interactions in embedded processor designs.

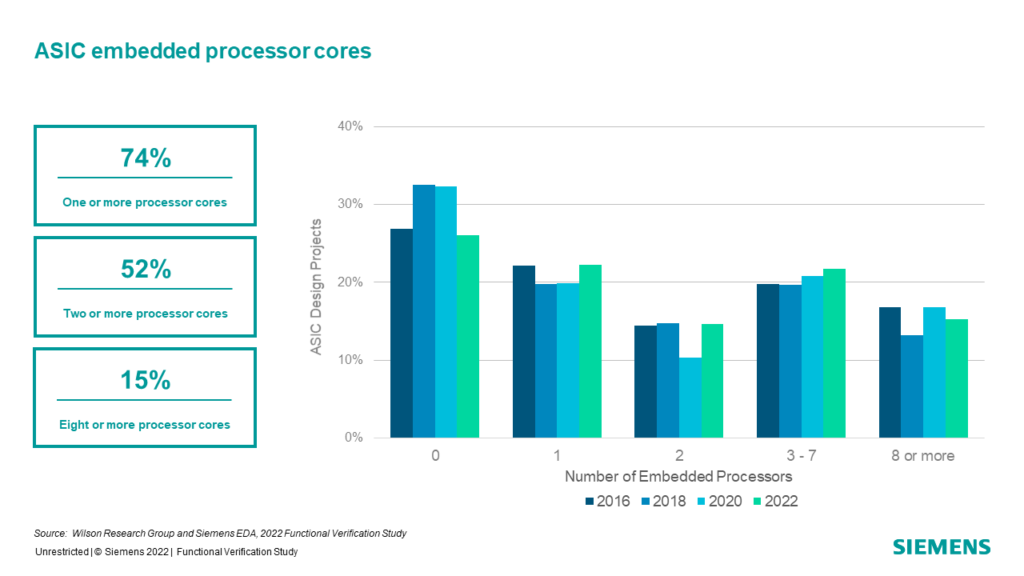

IC/ASIC Embedded Processors

What has changed significantly in design since the original Collett studies is the dramatic movement to SoC class of designs. In 2004, Collett found that 52 percent of design projects were working on designs that contain one or more embedded processors. Our 2022 study found that 74 percent of design projects were working on designs with embedded processors, as shown in Fig. 7-2.

Another interesting trend is the increase in the number of multiple embedded processes in a single SoC. For example, 52 percent of design projects today are working on designs that contain two or more embedded processors, while 15 percent of today’s designs include eight or more embedded processors. SoC class designs add a new layer of verification complexity to the verification process that did not exist with traditional non-SoC class designs due to hardware and software interactions, new coherency architectures, and the emergence of complex network on-a-chip interconnect.

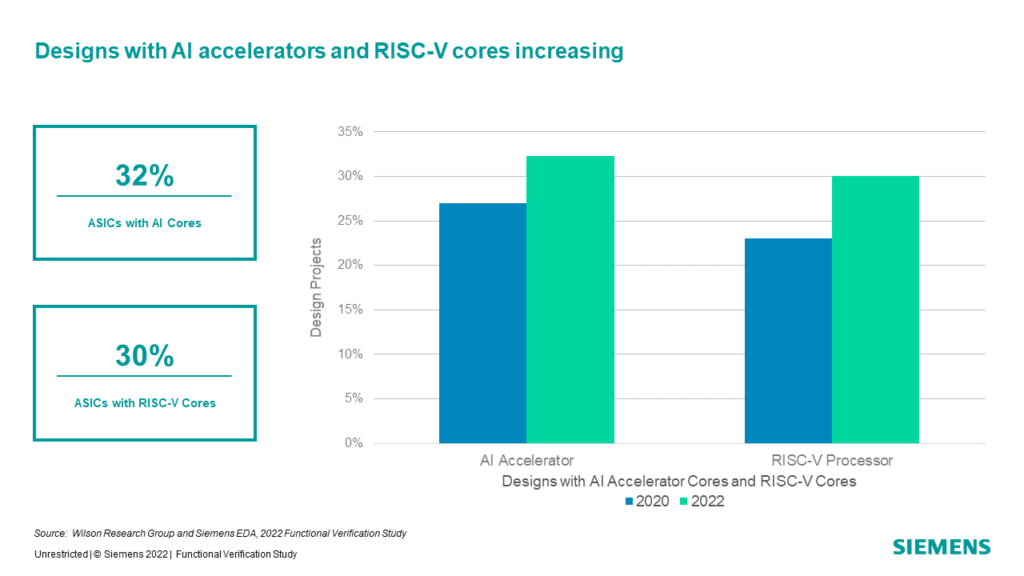

IC/ASIC Designs Incorporation AI and RISC-V Processors

Our 2022 study continued to track the number of IC/ASIC projects that have incorporated a RISC-V processor in their design, which was 30 percent, as shown in Fig. 7-3. In addition, we tracked the number of ASIC projects that have incorporated some type of AI accelerator processor (e.g., TPU, etc.), which was 32 percent. Both RISC-V and AI core increased from our 2020 study.

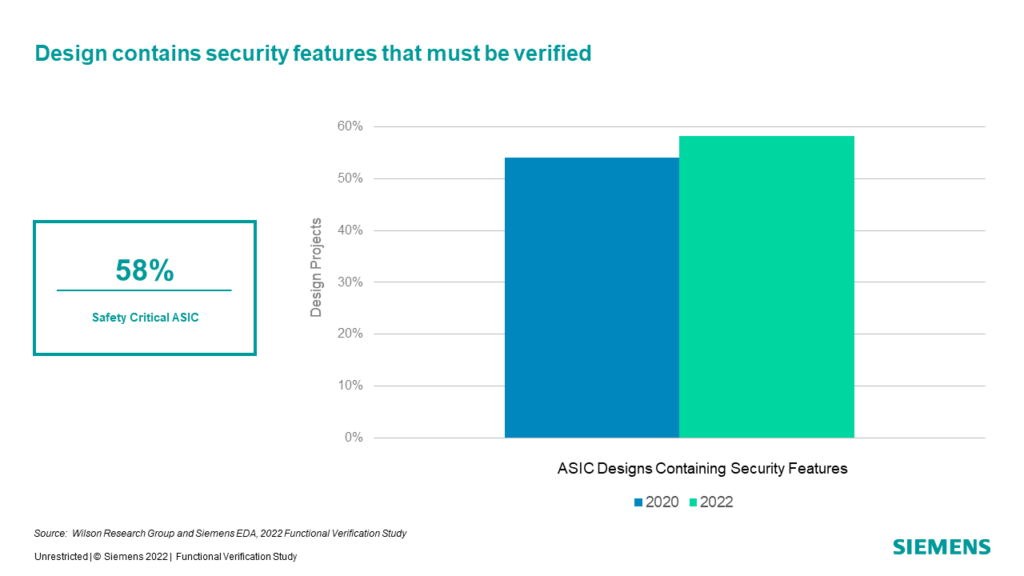

IC/ASIC Security Features

Many projects are implementing security features in their designs, as shown in Fig. 7-4. Examples of security features include security assurance hardware modules (e.g., a security controller) that are designed to safely hold sensitive data, such as encryption keys, digital right management (DRM) keys, passwords, and biometrics reference data. These security features add requirements and complexity to the verification process.

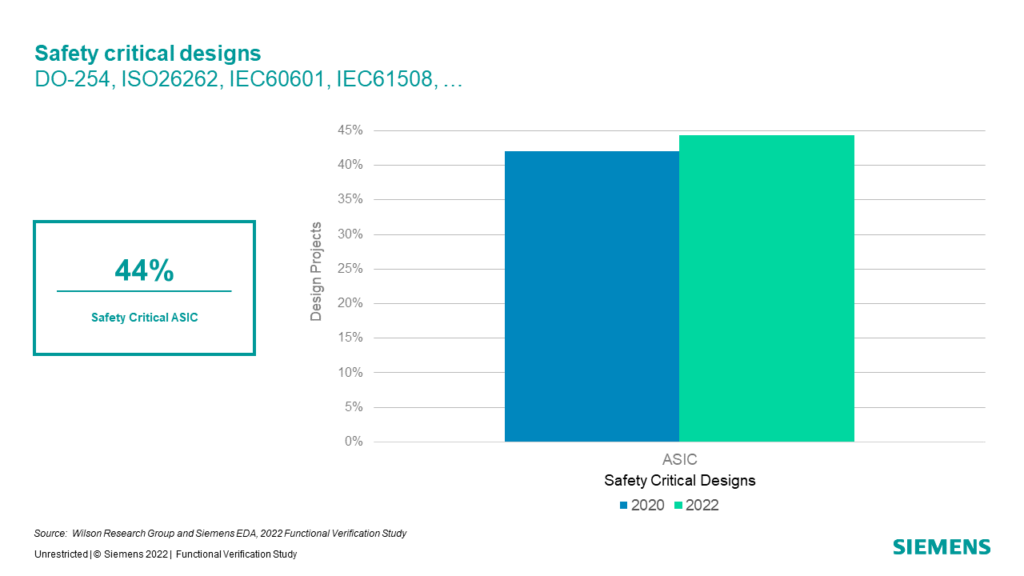

IC/ASIC Safety-Critical Design

Another example of increasing requirements contributing to complexity relates to safety-critical designs. In Fig. 7-5, we see an increase in the number of IC/ASIC projects working under one of multiple safety-critical development process standards or guidelines.

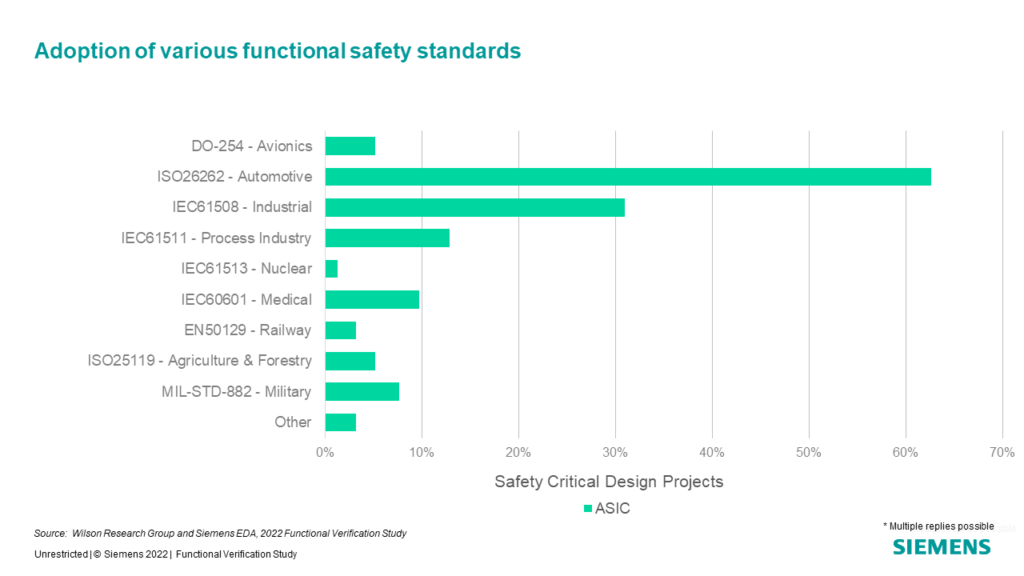

For those projects working under a safety-critical development process standard or guideline, in Fig. 7-6 we show the specific breakdown for the various standards within this group. Note that some projects are required to work under multiple safety standards or guidelines. For example, IEC61508 and IEC61511.

The key takeaway from this blog is that IC/ASIC designs are growing in complexity, which impacts verification effort and effectiveness.

In my next blog, I plan to discuss the growing IC/ASIC design project resource trends due to rising design complexity.

Quick links to the 2022 Wilson Research Group Study results

- Prologue: The 2022 Wilson Research Group Functional Verification Study

- Part 1 – FPGA Design Trends

- Part 2 – FPGA Verification Effectiveness Trends

- Part 3 – FPGA Verification Effort Trends

- Part 4 – FPGA Verification Effort Trends (Continued)

- Part 5 – FPGA Verification Technology Adoption Trends

- Part 6 – FPGA Verification Language and Library Adoption Trends

- Part 7 – IC/ASIC Design Trends

- Part 8 – IC/ASIC Resource Trends

- Part 9 – IC/ASIC Verification Technology Adoption Trends

- Part 10 – IC/ASIC Language and Library Adoption Trends

- Part 11 – IC/ASIC Power Management Trends

- Part 12 – IC/ASIC Verification Results Trends

- Conclusion: The 2022 Wilson Research Group Functional

- Epilogue: The 2022 Wilson Research Group Functional