How do you spell UVM? Opportunities in professional development.

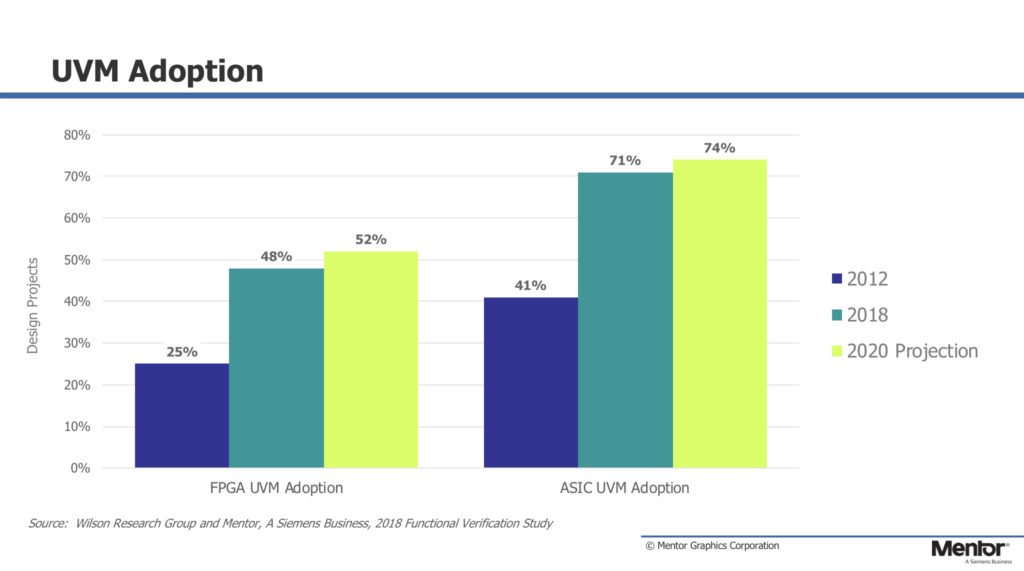

A few months ago I had the honor of being invited to lecture a graduate-level course on functional verification. After my lecture I was asked by a group of students if I could recommend specific skills that would be sought after by industry. I gave a tongue-in-cheek reply, which was “yes, learn to spell UVM.” Humor aside, my point is that engineers with UVM skills are in high demand. In fact, today we find that 71% of all ASIC projects and 48% of all FPGA projects have adopted UVM for testbench development.

And my advice for verification engineers seeking professional development suggestions is similar. Anything that you can do to enhance and sharpen your UVM skills will benefit both your career and your project.

With that said, I am excited to announce an outstanding upcoming technical web-seminar: UVM Coding Guidelines: Tips & Tricks You Probably Didn’t Know, which will go online at 8:00 AM Pacific Time on Friday April 10, 2020. But perhaps what I most excited about is that this web-seminar will be presented by our own subject matter expert, Chris Spear. Chris is one of the leading industry experts on both SystemVerilog and UVM, and co-authored the 2012 best-selling book “SystemVerilog for Verification.” Chris recently co-authored a paper with Rich Edelman titled “UVM – Stop Hitting Your Brother Coding Guidelines,” which won 2nd Best Paper Award at DVCon US 2020.

In this web-seminar, Chris Spear presents coding guidelines for UVM, and recommends how to create testbench transactions and component classes that are easily debugged and reused. He presents a set of rules for SystemVerilog coding to prevent many common bugs. These strategies are based on decades of his personal experience with functional verification in Verilog, SystemVerilog, and verification methodologies including UVM, OVM, VMM, and more.

So, if you are looking to sharpen your UVM skills, I highly recommend attending the upcoming UVM Coding Guidelines: Tips & Tricks You Probably Didn’t Know online web seminar. Also, we have a wealth of professional development technical courses, on-demand seminars, methodology cookbooks, and technical papers that are free out on the Verification Academy covering all aspects of functional verification. Check it out!