Going from “Standards Development” to “Standards Practice”

Historical Perspective

In my early days of standards development, I was intrigued how a standard went from the development phase to use phase. New standards were heralded with great fanfare but were also followed very quickly with books and other material to allow the “mere mortal” to understand what the IEEE standards prose meant and how best to use it. Everyone had their favorite VHDL book and I think I have them all!

What was clear to me was the IEEE standard was not sufficient to practice or understand the standard. After all, examples were few and far between in the standard. And even if there were examples in the standard, you were reminded that they are not part of the official standard – or in standards-speak – they are nonnormative.

User groups were popular too and continue to be today. VHDL International (now Accellera) had this notion of local VHDL user group chapters. When it came time to drive adoption of the VHDL gate-level library standard (known as VITAL), I attended several user group meetings to share details on how to use the new standard. I even solicited the support of a VHDL notable to put together a seminar series that would help ASIC library makers build their libraries. We took the seminar around the world and met with all the top ASIC suppliers. We even took our product that implemented the standard to the Cloud – while we did not call it the Cloud at the time. We had a model validation service in the early days of the internet that could be used to run training examples to validate ones own understanding or even test models and concepts to see if they would work. Free evaluation software was still a thing of the future then. As one byproduct of that work, we did have one competitor inundate us with the 1000’s of VHDL tests. We did throttle back their access to be fair to the others. But at that time, we left few ideas unexplored on how to drive global use and adoption of that standard.

Lessons Learned

What I understood was crossing the chasm from standards development to practicing the standard meant we had to build the knowledge, expertise and confidence in the user community to help them accept the standard and adopt it. I also learned that the standards developing organizations were not the best equipped to help practice the standard. The simple reason for this is the SDO is in place to bring together competitors to collaborate on the development of the standard but not foster competition on algorithms to best use the standard. This is perhaps better said by Synopsys’ Karen Bartleson in her “First Commandment for Effective Standards: Cooperate on Standards; Compete on Tools.”

Today’s Challenges with UVM & OVM

We are at that chasm with Open Verification Methodology (OVM) and the Universal Verification Methodology (UVM) today. While some may suggest OVM & UVM sit in a homogenous world where it works the same everywhere, the effective practice of the standards is anything but that. There are competitive options for users to explore and they are not ideas best promoted by a standards group. Mentor’s Mark Olen points out the value of an advanced method to generate stimulus rather than relying on the methods built into OVM & UVM in his recent blog post. Mark shows how a user gains 10x-100x in efficiency all the while doing this from within their OVM or UVM testbench.

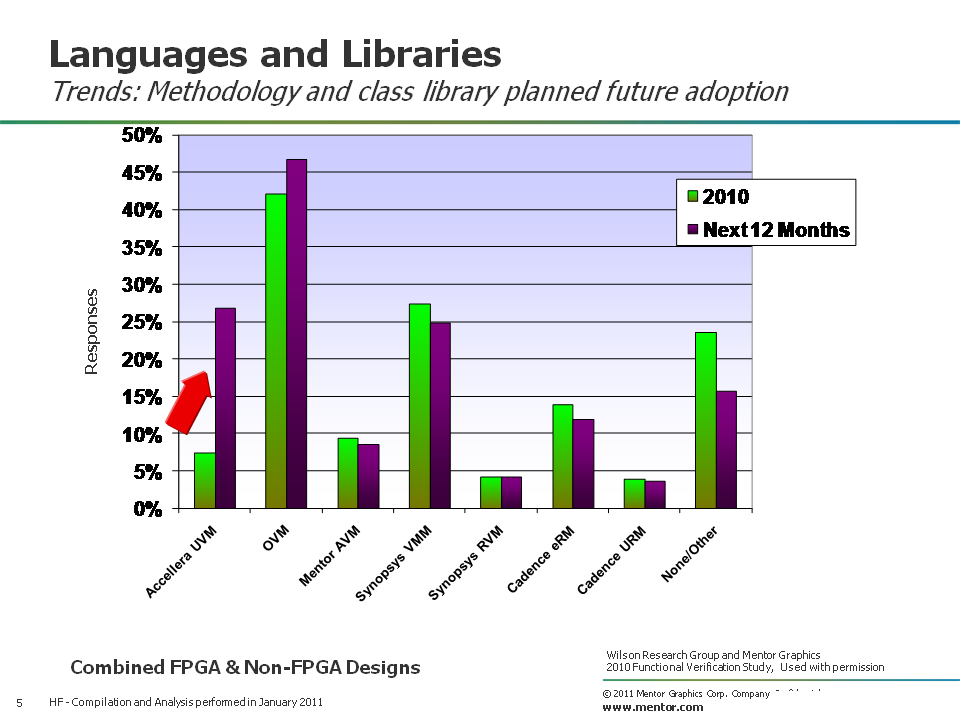

Mentor has thought long and hard about how to best get this information to users and how to help them practice OVM and UVM better than they can if they only had access to the lowest common denominator of information. We first did a blind survey to see what methodology the design and verification community was using now and what they were going to use 12 months from now to validate our focus on OVM and UVM. Mentor’s Harry Foster has shared a lot of detailed information on this already. If you have not read his blog postings on this yet, you should start with his prologue that outlines the survey.

Survey Says:

The survey clearly showed that UVM was in its ascendency and OVM was going to maintain strong and growing domination into 2012. Other survey results also clearly point out that SystemVerilog is the language of choice. While the survey shows what the user is doing, the standards developers were all collaborating on UVM and giving little time to OVM.

A Little Attention Goes a Long Way

While users were focused on continued use of OVM and planning for major move to UVM in 2012, the community developing standards had all but shifted to UVM, seemingly abandoning OVM. OVM was in need of care and attention given its dominant position in planned and future use.

Mentor stepped into the breach and has brought OVM into a strong, user-centric home that preserves the OVM World openness and augments it with several levels of additional user benefits in the Verification Academy. It also joins OVM and UVM in a single location that would not be appropriate in a standards body. After all, UVM is the standard from Accellera, not OVM. The Verification Academy also opens the cross pollination of ideas between the OVM and UVM users so one group can learn from another. We also brought the SystemVerilog User Group (SVUG) into the forum as well since OVM and UVM are based on the SystemVerilog language.

As we brought all these groups together, we did get many questions about Verification Academy Access Levels. First off, we dropped the OVM World requirement to register to download OVM. UVM and VMM were allowing anonymous downloads, so we made it the same for OVM. Of the 15,000+ OVM World registrants, most registered to download OVM. Just as OVM can now be downloaded without registration, the forums can be accessed in read-only mode without registration as well.

For those who used their OVM World registration to post on the forum, we moved them to “Forum Only Access” members so they could continue their posting privileges. The highest level of membership is “Academy Total Access.” Membership at this level is restricted to those who give a valid business profile. It enables access to training material, courses and lessons to help build SystemVerilog, OVM and UVM skills. It also allows users to gain knowledge about the advance algorithms that can help them get the 10x-100x or more out of OVM and UVM over conventional use. Below is a table of Verification Academy membership levels and privileges:

| Level | Privileges |

| Observer | Read-Only Forum Access. Free OVM/UVM kit download. No registration required. |

| Forum Only Access | Post to Forum and contributions area. Registration with any credentials required. |

| Academy Total Access | Total access. All academy areas open for free use. Registration with valid business profile. |

The response to this has been outstanding. While we strongly urge those who wish to develop the UVM standard to visit www.accellera.org and its www.uvmworld.org site to monitor that work, Verification Academy seems to have a much larger community of users with which to interact. And we will keep the Verification Academy current with the most recent versions of OVM and UVM. As of late July 2011 we recorded the following statistics.

| Forum | Members |

| Verification Academy Forum | 5,476 |

| UVM World Forum | 685 |

| VMM Central Forum | 696 |

We look forward to continue to develop the site and add to the richness of its content and continue to improve your experience with it. Your comments on how we can improve it are always welcome.