Progressive verification: A 3-step approach to post-layout signal integrity analysis

Maximizing design signal integrity with progressive verification

I’ve always felt that verifying a PCB layout before sending out for fabrication is a lot like flossing your teeth; everyone knows they should do it, but a lot of people just don’t. Those that don’t tend to have excuses for not doing it, but they aren’t necessarily good excuses.

Admittedly, that may be where the analogy ends. Unlike flossing, fully reviewing layouts is hard, time consuming, and involves the work of multiple experts across multiple domains. But similar to flossing, it occurs at a time when you just need to get going and would rather be investing your time in something deemed as more productive, because, as usual, you are behind schedule.

Time waits for no one

Siemens recently commissioned a study on the PCB design cycle which showed that OEMS averaged 38 designs per year, spending roughly 2.5 months on the design. These numbers were consistent regardless of the size of the organization, while large enterprise customers designed more complex boards with larger layer counts, the 2.5 month turn-around time per design was exactly the same as smaller organizations.

There is very little time to spare in our workflows. Once PCB layout is complete, you have entered a point in the product lifecycle where the clock is ticking and additional delays aren’t welcome.

So, how can you fully perform post route verification on your designs while maintaining your project’s timeline?

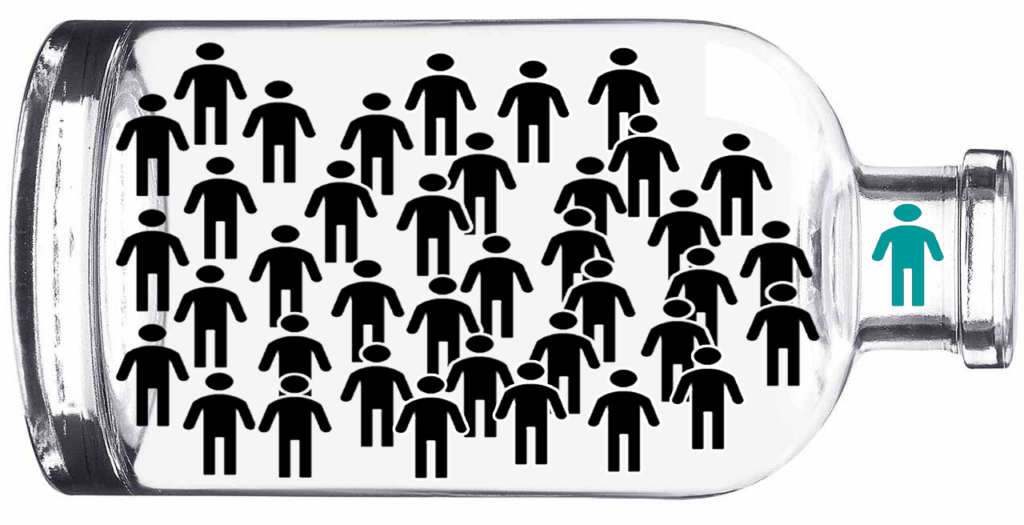

The expert crunch in post-layout verification

Traditional post-route verification reviews are based on hiring external experts, relying on in-house experts, or just simply visual inspections. External experts are expensive, internal experts are overwhelmed and visual inspection is a long, inaccurate slog that’s not guaranteed to find all the problems that exist.

This results in a bottle neck within the workflow. The time and money it takes for lab debug, rework and rebuilding the board far exceed the time and cost for validating properly to begin with, especially when it is possible to avoid this analytical overkill using a practical, progressive verification methodology.

Progressive verification is a dynamic and strategic approach to verification that allows internal design teams to efficiently manage their resources and reduce the risk of project delays, without putting all of the work on your busy engineers. It allows non-experts to find simple errors as early in the validation process as possible, allowing Subject Matter Experts (SMEs) to focus exclusively on the complicated SI issues that arise, optimizing the entire verification process.

The Progressive verification approach: Prioritizing for success

Progressive verification prioritizes analysis based on their ease of completion. It focuses on getting the simple stuff out of the way as quickly as possible, tackling those big problems that can be identified quickly first and then sifting through progressively finer and more granular issues.

The goal is to keep your Signal Integrity Engineer focused on issues that demand their expertise and not have them spend any time thinking about simple routing errors, or reviewing designs that don’t meet compliance specs. IBIS-AMI is timing consuming and complicated, but it is also recommended. It is because of this complexity, the expertise and time involved that we believe it should be performed on a pre-screened design that has been debugged prior to this significant time investment.

The process is straightforward:

- Quick tasks first: Automated Design Rule Checks (DRC) can be performed and resolved by a designer in a matter of minutes. Automating this process removes the fatigue and provides ‘another set of eyes’ on the design.

- Intermediate tasks next: Protocol Compliance Analysis handles the questionable DRC issues and works to discover new ones without the need for in-depth understanding of the specifics behind the standards themselves.

- Complex tasks last: Use SI experts for detailed modeling and vendor-specific component models and settings – only after simpler issues are resolved.

This approach ensures efficient use of time and resources, focusing expert efforts on the most challenging problems.

What are we looking for?

When we are doing this progressive verification approach – what is it that we are looking for?

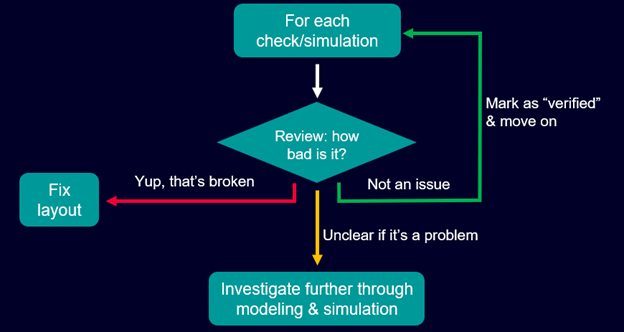

The decision flow for each step of the progressive verification process is also streamlined. For each rule we check, or simulation run, we stop and ask ourselves, how bad is it? If it is obviously broken or obviously fine, the outcome is also obvious, you either fix it or skip it. If we are unsure if it is a problem or not, then we will investigate it further through iterative modeling and simulation.

Implementing progressive verification in a post-route analysis workflow

When changing the workflow to adopt new tools or methodologies, it’s advisable to approach the transition gradually. Doing so provides 4 solid advantages:

Incremental implementation: Instead of overhauling the entire workflow at once, begin by integrating the new tools or methodologies into the first stage of your progressive verification process. This allows for a smoother transition and reduces the risk of disruption.

Controlled testing: Start by verifying the effectiveness of the new tools or methodologies in a controlled environment. This means testing them in a small, manageable part of your workflow to identify any issues or improvements needed before a full-scale implementation of progressive verification.

Utilize existing tools: You don’t necessarily need to invest in new tools immediately. Often, the tools you already have can be used to support the new methodologies. This can save time and resources while still allowing you to benefit from the new approach.

Feedback and adjustment: Collect feedback from the team during this initial stage. Use this feedback to make necessary adjustments to the new tools or methodologies. This iterative process helps in fine-tuning the workflow before broader implementation. Training and support: Provide adequate training and support to the team during this transition. Ensuring that everyone is comfortable and proficient with the new tools or methodologies is key to a successful implementation.

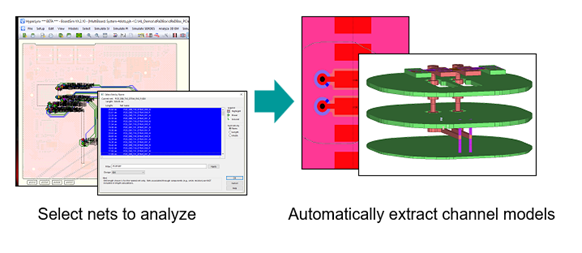

HyperLynx’ automated cut and stitch performs automated flow extraction on selected nets, without the need to isolate, test and refine these individual areas. By not requiring individual areas to be solved independently like contemporary signal integrity solutions, HyperLynx is able to analyze all of the channels, not just a subset of those channels, and do it very quickly.

Learn more about signal integrity

To learn more about the post-route progressive verification process with HyperLynx, join our webinar: Saving time and money with progressive verification In it, one of our HyperLynx experts will explore how to performing basic DRC checks during layout, how to use protocol compliance when verifying serial links, and how IBIS-AMI models can establish device programming signal integrity settings for system use.

You can also download our new eBook Progressive verification: a practical and effective approach to PCB design verification for a deeper dive into the strategy and ways to implement it.