Tessent BISR controller doing a lot more than memory repair

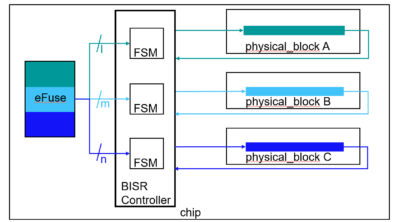

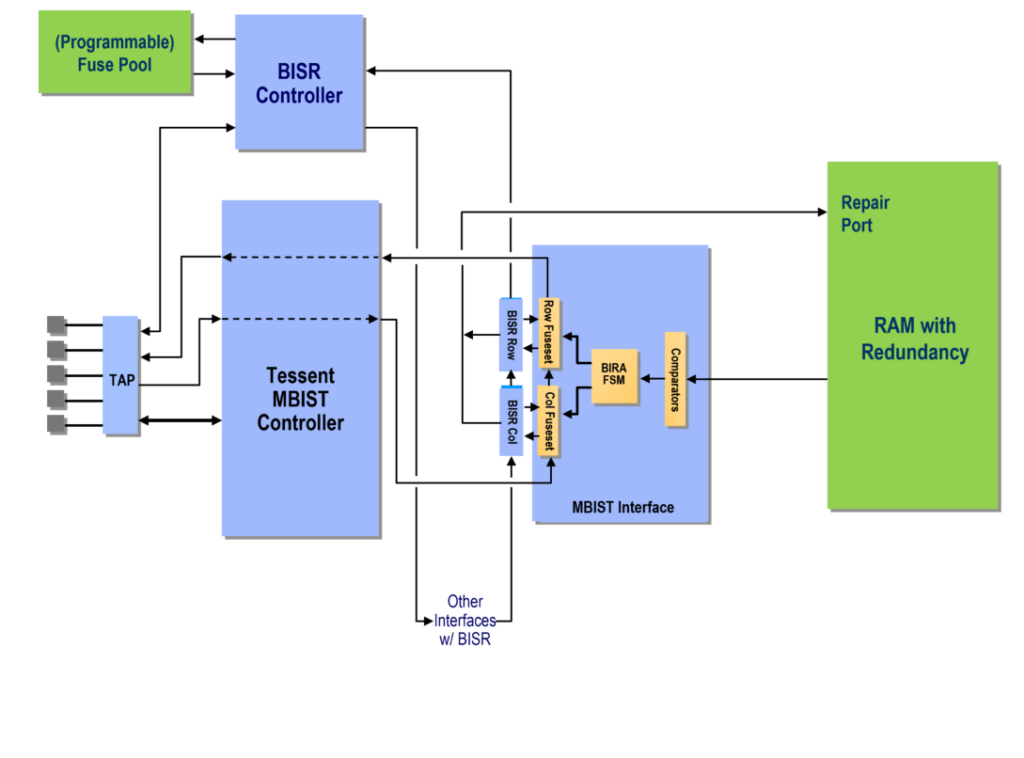

The BISR controller is at the heart of the Tessent Platform repair solution. It facilitates access to the BISR chains and the EFUSE. It also makes the autonomous repair at chip powerup possible. The normal repair structure looks something like the following:

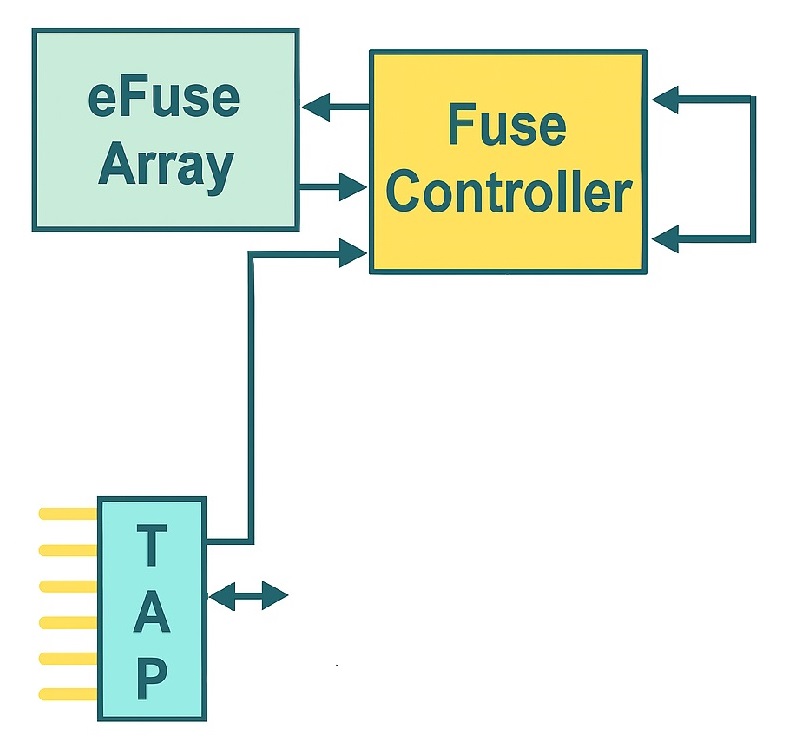

However, when used as an IJTAG instrument it can do so much more. For example, one potential use case that does not have anything to do with repair is using it to extract device/chip id data, wafer lot number, etc from an on-chip EFUSE or OTP. Without having any repairable memories or BISR chains in the design, a BISR controller can be added to function as an IJTAG instrument and allow a user to shift in or out any data stored in (typically a non-volatile) memory via the IJTAG network.

In this mode, the fuse_box_access method is used to write or read the storage device. For this specific configuration, there could be some implicit limitations which are determined by the other Tessent IPs added to your design. For example, above I mentioned that when the BISR controller is used explicitly as an IJTAG instrument, it takes advantage of the IJTAG network inclusive of the TAP controller to load and unload data into and from the chip. Typically, a user would only have access to the TAP controller during the manufacturing process. Consequently, that would limit when the BISR controller extracted data can be loaded/unloaded. The fact is though, this limitation is neutralized if the design has a Tessent Mission Mode (AKA: InSystem Test [IST]) controller since it affords full access to the TAP controller for the whole life of the device. Also, as is the case with the standard BISR repair flow, you would need to have an Interface module to facilitate communication between the BISR controller and the EFUSE or OTP. The good news is, if you are using one of the newer TSMC EFUSE, the interfaces are included as part of the Tessent Shell installation. Otherwise, for other vendors, the user is responsible for providing that. And, in general, from a flow perspective, there are minimal deviations from the usual steps in the Tessent BISR flow. The detailed process for this potential use case is captured in the following Tech Note that can viewed or downloaded from the Siemens Support Center site with your user account and credentials:

Use the BISR controller to access the EFUSE for only non-repair functions