Introduction to Tessent Multi-Die

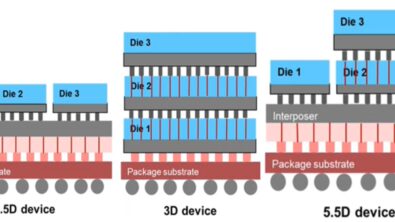

With the latest developments in the electronic industry, supporting revolutionary complex systems such as Autonomous vehicles or AI products/chips system-in-package becomes inevitable. System-in-package, SiP, which is “more than Moore’s law,” incorporates multiple dies inside one package, making heterogeneous integration possible. In a SiP, each die connects to other dies using either 2.5D or 3D interconnect technology. The key differences between 2.5D and 3D devices are:

- Stacking: 3D device has true vertical stacking of dies, whereas 2.5D has dies placed on a horizontal plane.

- Interconnects: A 3D device uses Through-Silicon-Vias (TSV) technology for high-speed and low-power interconnects, while a 2.5D device uses wire bonding or flip-chip.

- Performance: 3D device offers higher performance due to reduced latency and increased bandwidth between the stacked dies.

DFT flow overview:

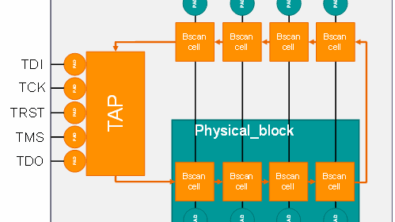

For multi-die designs, Tessent flow enables the insertion of BoundaryScan, MemoryBIST, OCC, EDT, and SSN hardware and scans, independent testing of the dies, retargeting internal modes from dies, and generating consolidated patterns to detect faults on die-to-die connections.

In 2.5D IC, we insert DFT logic in the dies to make the whole package compliant with the IEEE 1149.1 standard and insert the Boundary Scan in the die to improve its performance after integration into the package. Memory BIST and BISR can also be inserted in parallel with the Boundary Scan logic. Additionally, we insert test logic instruments for logic tests and ATPG. The SSN allows daisy chaining of the dies and is recommended for flexible testing of each die.

In 3D IC, we support the IEEE 1838 standard that describes the test access architecture and provide the required serial access mechanism using a Primary Test Access Port (PTAP) or Secondary Test Access Port (STAP). Flexible Parallel Port (FPP) access mechanism can be used to distribute volumes of scan patterns. Tessent SSN can be used as the Flexible Parallel Port (FPP) for the standard.

We can also use 3D and 2.5D methodologies together in the same package to create a 5.5D design that benefits from both methods. The Tessent Multi-die User’s Manual provides more information on core-level and die-level DFT insertion and scan insertion.

Resources:

Multi-die user’s manual: Tessent Multi-die User’s Manual

Support Kit for 2.5D design : 2.5 Flow for Multi Die designs

Support Kit for 3D design : 3D Multi-Die Flow in Tessent Shell

Webinar 1 : Navigating Through the Tessent Shell MultiDie Flow

Webinar 2 : DFT for chiplets and 3D IC’s using Tessent Multi-die

For Support and training information on Tessent Multi-die, please refer to Support center https://support.sw.siemens.com and Siemens’ Xcelerator Academy ( https://training.plm.automation.siemens.com/index.cfm)

Register to our upcoming EDA Expert Series Webinar