Effortless Embedded TAP Controller Insertion Tessent Platform

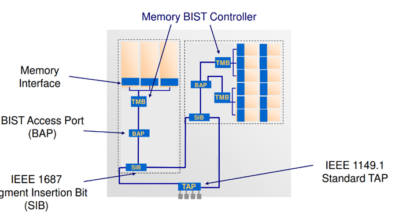

A tap controller, or Test Access Port (TAP) controller, is a critical component in the design-for-test (DFT) methodology used in integrated circuits. It is part of the JTAG IEEE 1149.1/ACJTAG 1149.6 standards and enables effective testing, debugging, and programming through a standardized interface.

Typically, TAP controllers are added at the chip level in a System-on-a-chip (SoC) designs. However, there are several reasons why you may want to insert the TAP inside a lower-level physical block.

Local Control: Having the tap controller at the block level allows for more precise control and access to signals within that specific block, which can lead to improved timing closure, reduced area congestion, and higher test coverage.

Isolation of Testing Impact: By containing the tap controller within a block, any test-related impacts can be confined to that block, minimizing disruptions to the rest of the chip and preserving overall chip performance.

Improved Test Coverage: The embedded tap controller enhances access to internal nodes, allowing for more comprehensive testing and potentially higher fault coverage.

The Tessent Platform EDA tool supports embedded tap controllers in a completely automated flow at all hierarchical levels, from the lower-level physical block implementation to the chip-level design integration, BSDL creation, and BoundaryScan pattern generation.

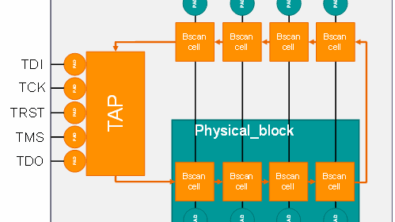

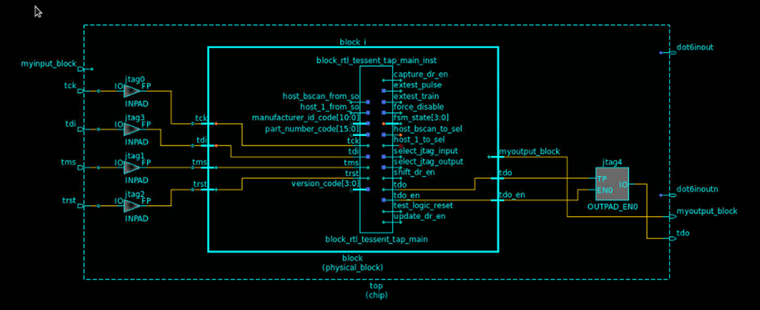

In the first pass, the tap controller is first inserted inside the physical_block, and the tap signals are brought up to the block-level interface. In the next pass, the chip-level integration is performed, and the tap ports are connected to chip-level pads. (Refer to the schematic below that shows the main tap controller inside “block_i”, and all the TAP ports (tck, tdi, tms, trst, tdo, tdo_en) are connected from the chip-level external pads to the tap ports inside the block.)

Finally, the BSDL file is extracted, and boundary scan patterns are generated for the chip.

There are many advantages of using Tessent for your embedded TAP implementation, including:

Reduced Test Time: Tessent Automated test insertion reduces manual effort and accelerates the overall test process, leading to quicker turnaround times for design verification.

Enhanced DFT Capabilities: Tessent provides robust design-for-test (DFT) features that improve the controllability and observability of signals within the design.

Streamlined Integration: The tools facilitate easy integration of the embedded tap controller into existing designs without significant redesign efforts.

Compatibility with Various Standards: Tessent supports various standards for scan and test access, ensuring broad compatibility with industry practices.

Scalability: Tessent’s solutions are scalable, suitable for small and large designs, and accommodating evolving project requirements.

For complete details on how to insert a Tap Controller inside a physical block, including a full testcase for download, refer to the Knowledge-based TechNote below in the Tessent Support Center: