Meeting the challenges of reliability verification for the era of 3D ICs

By Keerthana Chelur Hithesh

No one likes surprises during chip tape-out—especially when they threaten your project’s reliability. Electrostatic discharge (ESD) failures are a persistent and costly issue in integrated circuit (IC) manufacturing. Researchers at Imec estimate that ESD-related problems account for almost 40 percent of all IC failures. As the global 3D IC market surges toward 32 billion by 2030, design teams face a critical challenge: conventional reliability verification methods are no longer sufficient for advanced multi-die architectures.

This blog unpacks the hidden reliability crisis emerging in advanced 2.5D and 3D ICs, explains why conventional verification fails and explores how Siemens EDA tools, Innovator 3D IC and Calibre 3DPERC, address these challenges. Let’s dive into how you can transform complexity into a competitive advantage with smarter, system-level verification.

Why 2.5D and 3D ICs are reshaping reliability standards

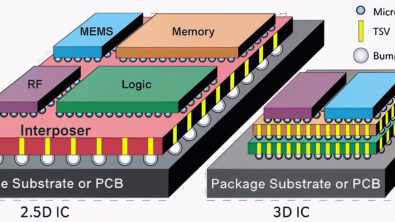

2.5D and 3D integrated circuits promise unmatched performance, reduced power consumption and more features in smaller form factors. Yet, the complexity of these designs is triggering a hidden verification crisis. The industry’s evolution from traditional 2D ICs to dense 2.5D and stacked 3D architectures is not simply a step forward—it’s a paradigm shift that exposes flaws in legacy verification flows. Figure 1 shows simplified depictions of 2.5D and 3D chip architectures.

The verification flows you’ve relied on for years are being outpaced by the rapid shift to multi-die designs. Traditional methods built for single-die architectures can’t keep up with the intricate interactions, diverse technology nodes and vendor ecosystems involved in modern 3D ICs. If you’re responsible for ensuring reliability in the age of advanced semiconductors, you need practical insight into why your current tools may fall short—and discover what a purpose-built approach looks like.

The multi-layered reliability problem in 3D integration

Electrostatic discharge protection complexity

ESD protection is relatively straightforward in conventional 2D designs, with clear paths and predictable behavior. In contrast, 3D IC architectures create a maze of potential discharge routes, making traditional tools obsolete for accurate modeling and verification.

In 3D ICs, distinguishing between internal and external I/O connections is crucial. Internal stacked-die connections require distinct protection strategies. However, many verification tools treat all paths the same, which can lead to wasted area and power through over-protection or reliability risks through under-protection.

Inter-die connectivity verification challenges

Physical connections like through-silicon vias (TSVs), microbumps and advanced packaging techniques add new layers of complexity. Each connection can be a potential failure point, requiring analysis for resistance, current density and thermal factors. Connections often cross voltage domains, clock regions and signal types, multiplying verification requirements. Legacy point-to-point approaches become unusable amid the intricate web characteristic of modern 3D assemblies.

Siemens EDA reliability verification: Innovator 3D and Calibre 3DPERC

Recognizing these fundamental challenges, Siemens EDA has developed a flow that addresses the unique requirements of 3D IC reliability verification. The Innovator 3D IC flow, seamlessly integrated with Calibre 3DPERC, represents a purpose-built approach to system-level reliability verification for advanced multi-die assemblies.

Dual verification strategy for maximum flexibility

The Innovator 3D methodology employs both black-box and white-box verification strategies, allowing design teams to choose the appropriate level of detail based on their specific project requirements and timeline constraints. This flexibility proves essential in modern design environments where different project phases demand different verification approaches.

- Black-box verification provides rapid interface validation and high-level connectivity checks, enabling early-stage design decisions and quick iterations. This approach proves particularly valuable during initial design exploration and when working with intellectual property blocks where detailed internal information may not be available.

- White-box verification delivers comprehensive device-level analysis, providing the detailed insights necessary for final sign-off and critical reliability assessments. This approach ensures that no potential failure mode goes unexamined, providing the confidence required for high-stakes production decisions.

Streamlined workflow integration

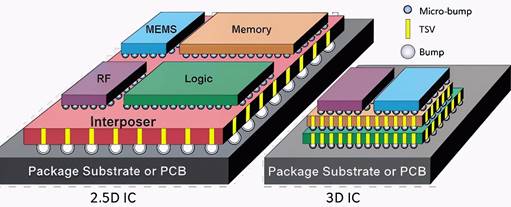

The integration between Innovator 3D and Calibre 3DPERC creates a seamless workflow that eliminates the traditional handoff challenges between different verification tools. Innovator 3D prepares the 3D IC design and generates compatible source netlists, which Calibre 3DSTACK then uses to construct comprehensive multi-die connectivity models.

This prepared model becomes the foundation for Calibre 3DPERC’s advanced reliability verification capabilities, including ESD path validation, point-to-point resistance analysis and current density verification. The seamless data flow between tools eliminates translation errors and ensures consistency throughout the verification process. Figure 2 shows the integrated tools used in this flow.

Addressing real-world 3D IC challenges

Vendor-agnostic

Modern 3D IC projects often involve components from multiple vendors, each with their own design methodologies, technology nodes and verification approaches. The Innovator 3D and Calibre 3DPERC solution provides a unified verification framework that ensures consistent reliability analysis regardless of the underlying technology diversity.

Scalability for complex assemblies

Verification tools must scale without compromising accuracy or performance. The Siemens solution addresses this challenge through optimized algorithms and intelligent partitioning strategies that maintain verification quality while managing computational requirements.

Quantifiable benefits for design teams

The implementation of comprehensive 3D IC reliability verification delivers measurable improvements across multiple dimensions of the design process:

- Faster design exploration: Enhanced verification speed lets teams evaluate more alternatives within project timelines.

- Reduced risk: Early, accurate reliability checks help avoid costly late-stage revisions and launch delays.

- Shift-left confidence: Early-stage verification lets teams make confident decisions and reduce iterative design cycles.

The path forward: Transforming 3D IC complexity into competitive advantage

As 3D ICs push the boundaries of performance and integration, robust reliability verification is essential. Siemens EDA’s Innovator 3D and Calibre 3DPERC solution empower teams to deliver reliable, high-performing products while successfully navigating multi-die complexity.

The future belongs to organizations that can successfully navigate the complexity of advanced multi-die architectures while maintaining the reliability standards that customers demand. With the right verification methodology, design teams can transform the challenges of 3D IC design into competitive advantages that drive innovation and market success.

Ready to revolutionize your 3D IC reliability verification process? Download the complete technical paper to discover how Siemens EDA’s Innovator 3D and Calibre 3DPERC solution can accelerate your time-to-market while ensuring uncompromising reliability standards.