Enhanced short isolation process for faster circuit verification

By Ritu Walia

Repetitive layout vs. schematic (LVS) runs can significantly delay project timelines. A huge number of shorted nets in the layout is a major cause of connectivity errors, comprising a huge part of LVS violations. With thousands of such connectivity issues to address, debugging these errors is time-consuming and labor-intensive, often requiring designers to switch between multiple environments for debug & LVS re-runs, disrupting their workflow and extending the required number of verification cycles.

This blog summarizes how the Calibre RVE ISI Flow along with the integration of Calibre nmLVS Recon with the Calibre RVE results viewer significantly enhances the LVS debugging process. This powerful combination enables faster and more efficient isolation and resolution of shorted nets, ultimately improving overall design quality and reducing time to market.

Understanding the challenges of LVS short isolation

The growing complexity of shorted nets

A single shorted net can involve multiple paths, and identifying the exact location of these shorts can be challenging. At advanced nodes like 5 nm, designs can contain over 15,000 shorts, making manual inspection and debugging impractical.

Manual inspection limitations

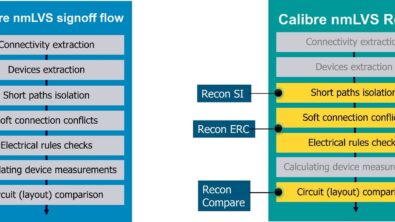

Traditional LVS debugging methods often involve switching between different environments: a graphical user interface (GUI) for short debugging and a command line interface for LVS re-runs. This context switching is not only inefficient but also prone to errors. Additionally, manual visual inspection of shorts across a large design with billions of components is both time-consuming and error-prone. Figure 1 shows the traditional LVS debugging flow that requires shifting between GUI and command line.

Highlights of key benefits of Calibre RVE interactive short isolation flow

Comprehensive visualization: The updated summary view in Calibre RVE groups shorted paths linked to each short into a tree view, making it easier for designers to isolate and fix them. This organized view helps find error-causing objects by focusing on what matters the most, helping designers quickly identify and address the most critical shorts.

Simulated fixes: Designers can simulate short fixes within the RVE environment without making actual changes to the design layout. This virtual removal of polygons allows for immediate validation of fixes, saving time and avoiding unnecessary full LVS re-runs until all shorts are addressed.

Parallel debugging: With the Background Verify Shorts capability, designers can debug multiple shorts simultaneously, improving efficiency and reducing overall cycle time. This parallel debugging of multiple shorts at the same time, allows for continuous workflow without waiting for individual short verification to complete.

Introducing Calibre RVE’s enhanced short isolation capabilities

Integrated verification

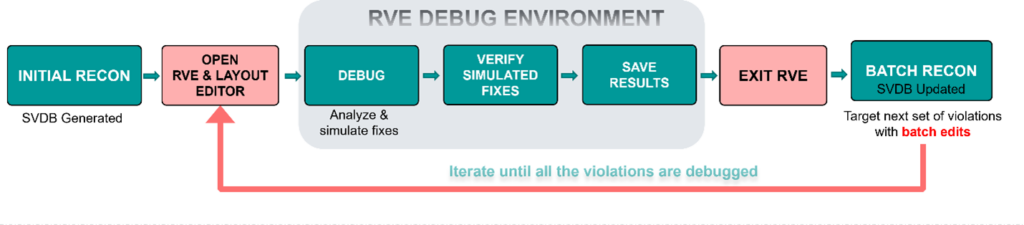

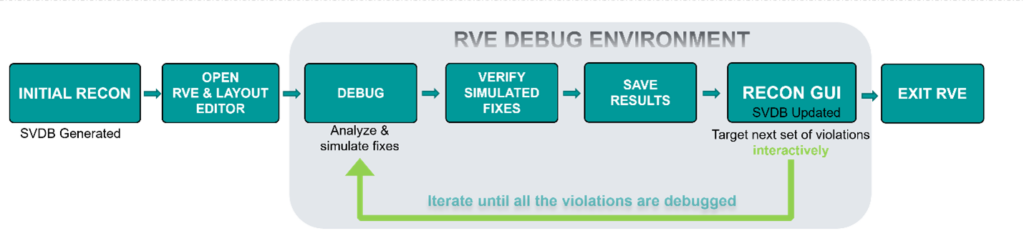

Calibre Interactive nmLVS Recon GUI is now integrated within the Calibre RVE results viewing environment (RVE) to streamline the RVE interactive short isolation (ISI) flow (figue 2). This integration promises to improve how designers handle LVS verification, particularly the isolation and debugging of shorted nets. The Calibre RVE ISI flow significantly reduces the need for context switching and manual inspection, making the entire process more efficient.

The Calibre nmLVS Recon GUI allows designers to run targeted LVS extractions directly from the RVE interface. This push-button functionality ensures seamless execution of short isolation and verification within a unified environment, eliminating the inefficiency of switching between different environments.

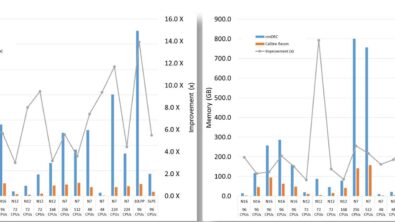

Achieving faster turnaround times

The integration of Calibre nmLVS Recon with Calibre RVE ISI is a game-changer for chip designers. It offers a streamlined, efficient, and visually organized method for short isolation and debugging, significantly reducing overall design turnaround time. By enabling targeted, layer-aware, and net-aware LVS runs, designers can achieve 6-10 times faster turn-around compared to traditional full LVS runs.

Improved productivity

Adopting the Calibre RVE ISI flow means less time spent on manual inspections and more on productive design work. This toolset not only enhances the debugging process but also supports early-stage verification, allowing for a cleaner design before the final full-chip LVS run. The result is a boost in productivity and a faster path to tape-out.

Highlights of key improvement in Calibre RVE interactive short isolation flow

The key features of the Calibre RVE ISI flow help designers shorten turnaround times and boost productivity.

Comprehensive visualization: The updated summary view in Calibre RVE groups shorted paths linked to each short into a tree view, making it easier for designers to isolate and fix them. This organized view helps find error-causing objects by focusing on what matters the most, helping designers quickly identify and address the most critical shorts.

Simulated fixes: Designers can simulate short fixes within the RVE environment without making actual changes to the design layout. This virtual removal of polygons allows for immediate validation of fixes, saving time and avoiding unnecessary full LVS re-runs until all shorts are addressed.

Parallel debugging: With the Background Verify Shorts capability, designers can debug multiple shorts simultaneously, improving efficiency and reducing overall cycle time. This parallel debugging of multiple shorts at the same time, allows for continuous workflow without waiting for individual short verification to complete.

Conclusion

For chip designers who work on debugging early-stage dirty layout designs, the enhanced Calibre RVE ISI flow offers a robust solution. It simplifies short isolation and debugging, integrates seamlessly into the design environment, and can contribute to reducing the number of LVS verification cycles. By adopting this approach, design teams can achieve faster, more efficient LVS verification, ensuring high-performing and reliable designs ready for the market, faster than before.

Discover the power of the Calibre RVE ISI flow and transform your LVS verification process today. Dive into the full technical paper to explore how these advancements can elevate your design workflow.

For more information on how Calibre solutions can help streamline your LVS debugging process, read the technical paper Faster short isolation with LVS Recon runs in Calibre RVE.

Visit our Shift left with Calibre solutions website and explore our comprehensive resource library.