Faster design verification with Calibre nmLVS Recon Compare

By Wael ElManhawy

Layout versus schematic (LVS) comparison is a fundamental step in integrated circuit (IC) design verification. It ensures that the physical layout of the circuit matches its schematic representation, verifying the correctness and functionality of the design. Traditionally, LVS comparison is performed during signoff verification, where dedicated tools compare layout and schematic data to identify any inconsistencies or errors. However, uncovering errors at the signoff stage leads to time-consuming iterations that delay design closure and time to market. While early-stage LVS comparison could mitigate these issues, it often generates millions of error results due to the incomplete status of the design.

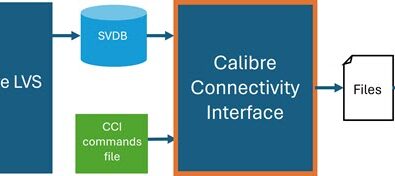

The Calibre nmLVS™ Recon Compare solution introduces an intelligent shift-left process for fast and precise LVS comparison earlier in the design cycle. It automates the black boxing of incomplete blocks and facilitates automatic port mapping, allowing designers to achieve faster LVS iterations on early-stage designs.

Challenges of LVS verification in early design stages

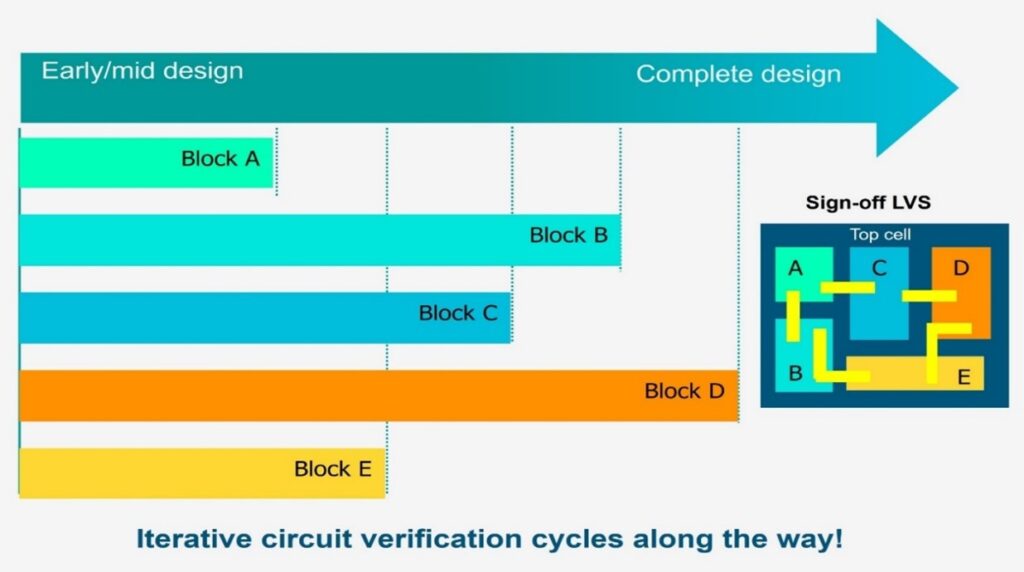

IC design involves multiple stages, from conceptualization to fabrication. Among these stages, designers must verify the layout against its schematic representation to ensure that the final product functions as intended. However, in the early stages of design, when many blocks are not yet finalized, performing a comprehensive LVS comparison is impractical. Using traditional methods of manual inspection or waiting until all blocks are complete delays the verification process and potentially leads to costly design errors (figure 1). Engineers need to verify that top-level connectivity is correct even before all blocks are finished to avoid any surprises later in the design process.

Calibre nmLVS Recon Compare: A game-changer

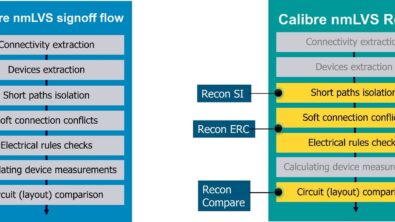

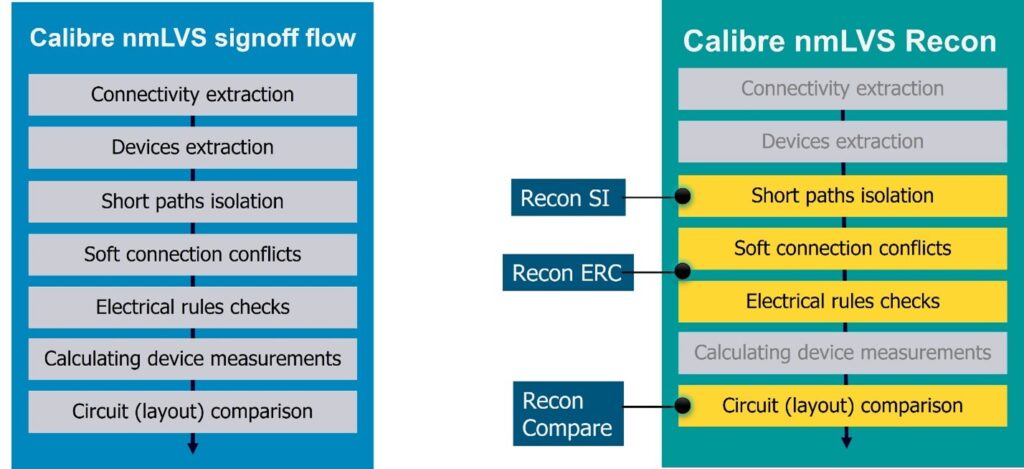

Calibre nmLVS Recon Compare leverages automation techniques to enable early-stage comparison between top-level layout and schematic representations. This intelligent execution focuses on resolving early design pain points, ensuring quicker iterations and efficient debugging while preserving the full mandatory signoff flow (figure 2).

Key steps in the Calibre nmLVS Recon Compare methodology

- Black boxing: Calibre nmLVS Recon Compare automatically treats incomplete blocks within the design as black boxes, abstracting their internal details while preserving their connectivity information. This allows the comparison to focus on the interaction between complete and incomplete blocks without getting bogged down by internal complexities. (For more on black boxing – watch this video from our “How To” Video Library: How to debug LVS BLACK BOX issues)

- Port mapping: The solution automatically maps ports between the layout and schematic representations, ensuring consistency and alignment. This mapping process identifies corresponding connections between blocks, facilitating accurate comparison despite incomplete designs.

- Comparison engine: Once black boxing and mapping are complete, Calibre nmLVS Recon Compare employs a comparison engine to analyze the layout and schematic data. Discrepancies, such as missing connections or mismatched components, are flagged for further investigation.

Advantages of using Calibre nmLVS Recon Compare

- Early detection of errors

By enabling early-stage LVS comparison, Calibre nmLVS Recon Compare facilitates the timely detection of errors and inconsistencies. This reduces the risk of design rework and costly delays, ensuring that design teams can address issues before they become critical. - Accelerated design verification

Automating the comparison process streamlines design verification, allowing designers to identify and resolve issues efficiently, even when all blocks are not finalized. This leads to faster overall circuit verification and reduces the time and effort required for manual inspection. - Improved collaboration

Calibre nmLVS Recon Compare promotes collaboration among design teams by providing a centralized platform for verifying design correctness and sharing feedback. This enhances communication and coordination, leading to more efficient design workflows. - Enhanced design confidence

By ensuring alignment between layout and schematic representations, Calibre nmLVS Recon Compare enhances designers’ confidence in the correctness and functionality of the final product. This confidence is crucial for meeting project deadlines and achieving successful design tapeouts.

Customer success with Calibre nmLVS Recon

Calibre nmLVS Recon has demonstrated significant benefits in real design projects. Customers have reported an average of 10x runtime improvements and 3x lower memory requirements. A verification team at Marvell, for example, enhanced their LVS flow over the full design cycle using Calibre nmLVS SI, achieving faster verification times and improved efficiency.

For more information, watch Marvell engineers describe their usage of Calibre LVS Recon and the shift-left strategy.

Integration with existing design workflows

Calibre nmLVS Recon Compare integrates seamlessly with existing design workflows, enabling incremental refinement of the overall design as individual blocks are completed. The tool’s user-friendly interface allows designers to specify comparison parameters and view results in a comprehensible format, facilitating efficient debugging and error resolution.

Conclusion

Calibre nmLVS Recon Compare presents a novel approach to early top-level layout versus schematic comparison in semiconductor design. By automating black boxing and port mapping, the solution enables designers to perform comprehensive verification even when all blocks are not finalized. This accelerates design verification, improves collaboration, and enhances design confidence in semiconductor design workflows.

As individual blocks are completed, Calibre nmLVS Recon Compare ensures consistency and correctness at each stage. During the debug phase, the tool helps identify and isolate errors by pinpointing discrepancies between layout and schematic representations. Future developments may involve further options for the comparison process and integration with emerging design methodologies to address evolving design challenges.

To learn more about how Calibre nmLVS Recon Compare helps IC verification engineers reduce the time and effort needed for physical and electrical verification on large designs, read the full technical paper: Accelerate design verification with Calibre nmLVS Recon Compare.