Securing your silicon: Why automated IP integrity is non-negotiable in modern SoC design

By Sara Khalaf, Product Engineering Manager

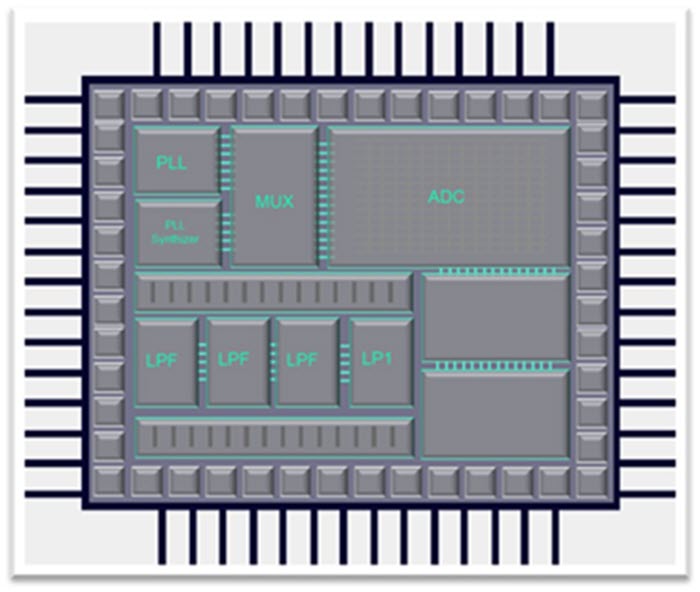

In the world of System-on-Chip (SoC) design, Intellectual Property (IP) blocks are the building blocks of innovation. Whether licensed from third parties, reused from internal libraries or custom-designed, these pre-verified components are the foundation of complex functionalities. They are typically treated as “black boxes,” expected to remain untouched from initial floorplanning through to final sign-off. But what happens when reality diverges from this ideal? What if these critical IP blocks are unintentionally altered during the physical design process, leading to costly re-spins, performance degradation or even functional failures?

The silent threat: When IP integrity is compromised

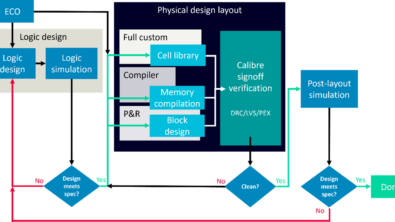

The journey of an SoC from concept to silicon is fraught with challenges. Modern design flows, with their intricate placement, routing and fill operations, can inadvertently introduce subtle yet critical changes to IP blocks. Crucially, these changes often go unnoticed because traditional DRC decks don’t capture these kinds of modifications, as in most cases they are DRC clean. Manual audits are simply not feasible at the scale of today’s SoCs.

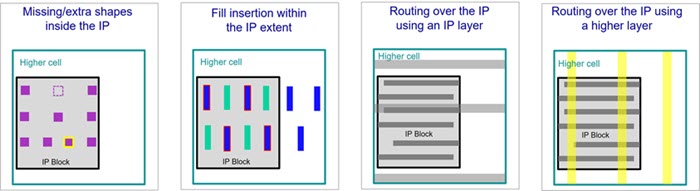

Consider these common scenarios where IP integrity can be compromised:

- Omitted guidelines: IP providers might miss specifying crucial placement, fill or routing restrictions, or designers might overlook enforcing them.

- Unintentional modification: Automated design tools, particularly during fill or routing optimization, can sometimes delete or insert shapes within IP blocks.

- Deviation from golden reference: During design handoff or integration, minor edits, omissions or label mismatches can creep into an IP block.

These “silent errors” often go unnoticed because they don’t necessarily trigger DRC violations. Yet, even minor, undetected differences can lead to significant issues, impacting performance, causing subtle functional failures or leading to unexpected manufacturing problems. The cost of discovering such issues late in the design cycle—or worse, after tape-out—can be astronomical, involving significant time delays and financial losses.

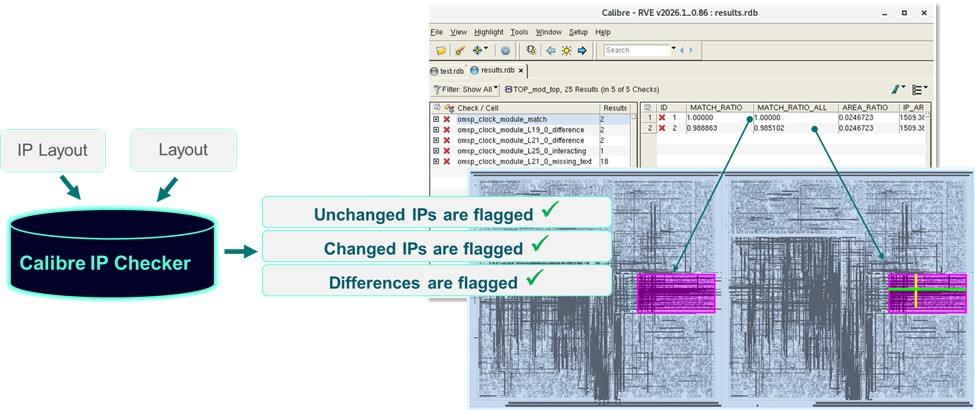

The solution: Automated IP integrity with Calibre IP Checker

To proactively address these critical challenges, Siemens EDA offers the Calibre IP Checker. Part of the comprehensive Calibre Pattern Matching tool suite, the Calibre IP Checker provides an automated, early and exhaustive solution for ensuring IP integrity. It meticulously compares every instance of an IP in the SoC against its original, golden reference, even after all physical design steps are complete.

How Calibre IP Checker safeguards your design

Calibre IP Checker integrates seamlessly into existing design flows, accelerating the “shift-left” approach by moving critical verification steps earlier in the design cycle. This proactive approach significantly reduces the risk of late-stage surprises.

Here’s how it works:

- Instance identification: The tool flags all locations where an IP appears in the final layout, regardless of instance naming differences from the library cell name.

- Comprehensive comparison: It performs a detailed comparison of all geometry and hierarchy within the extent of every IP against its original reference, identifying even the most minor mismatches.

- Modification flagging: Calibre IP Checker clearly reports whether each IP instance was modified and precisely pinpoints where deviations occur, whether internal to the IP or due to external interactions like routing or fill.

- Text validation: Crucially, it detects and flags any changes in labels or text objects. These seemingly minor alterations are a common source of cryptic Layout Versus Schematic (LVS) errors at sign-off.

Technical spotlight: Uncovering hidden IP issues

What specific problems can Calibre IP Checker find that traditional checks miss?

- Geometry alterations: Shapes within the IP are unintentionally deleted, moved or added after placement.

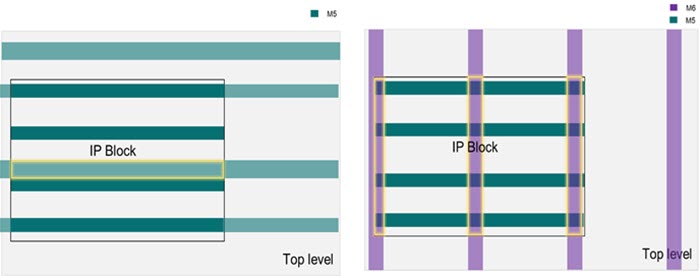

- Improper fill insertion: Top-level metal fill or other filler shapes are mistakenly inserted within IP regions, often because blockage layers weren’t honored or defined.

- Improper routing: Routes from higher metal layers or forbidden layers cross into or out of the IP area, degrading performance or violating foundry constraints.

- Text/label changes: Modifications or omissions in text objects and labels, which can significantly affect LVS outcomes and traceability.

Calibre IP Checker employs nuanced comparison logic, examining layer-by-layer, including shapes inside, over and even text on each block. This ensures that subtle and rare differences, which would otherwise escape traditional DRC or LVS, are promptly flagged for correction.

Beyond IP blocks: Flexible validation for standard cells and text

While its primary focus is complex functional IP blocks, Calibre IP Checker is also flexible enough to validate standard cells and text with customized logic. For instance, when validating standard cells, the tool can intelligently focus on cell contents, ignoring common over-cell routing in dense digital logic, while still verifying geometry and label integrity. This targeted approach ensures that verification efforts are precise and efficient, regardless of the component type.

Integrating IP checking into your SoC flow: The advantages

Integrating an automated IP integrity check like Calibre IP Checker into your physical design flow offers significant advantages:

- Early detection: Catching discrepancies before sign-off prevents time-consuming and expensive rework at tape-out. This proactive measure safeguards your project schedule and budget.

- Increased confidence: With every IP instance automatically checked, design teams can trust that their design intent and foundry compliance are preserved. This eliminates the need for tedious manual spot-checking and provides peace of mind.

Conclusion

As SoC complexity continues to escalate and the reliance on IP blocks becomes even more central, ensuring the integrity of each IP instance throughout the entire design flow is no longer an optional best practice—it’s a critical requirement. Automated solutions like Calibre IP Checker, part of the Siemens EDA Calibre Pattern Matching suite, provide the necessary confidence, speed and visibility for robust IP integrity verification. By seamlessly integrating this crucial step into the physical design flow, design teams can catch errors earlier, prevent costly re-spins and ultimately deliver reliable, high-performance silicon with fewer surprises at tape-out.

Further reading:

Technical Paper Guarantee IP integrity with Calibre IP Checker

Explore more on our website Siemens EDA solutions for physical verification