Enhancing IC Verification: Smarter solutions for faster, more reliable designs

By Jonathan Muirhead

Modern chip layouts are more intricate than ever, incorporating a mix of custom and third-party intellectual property (IP) blocks. Ensuring the integrity and symmetry of these intricate layouts is critical to device performance, reliability and manufacturability. Traditionally, verification tasks such as IP checking and symmetry validation have relied on block designers using correct-by-construction techniques, with final checks by visual inspection and DRC sanity rules late in the design cycle. However, this late-stage approach can lead to delays in final tape out meaning slower time-to-market and worse yet poor device reliability and even failure.

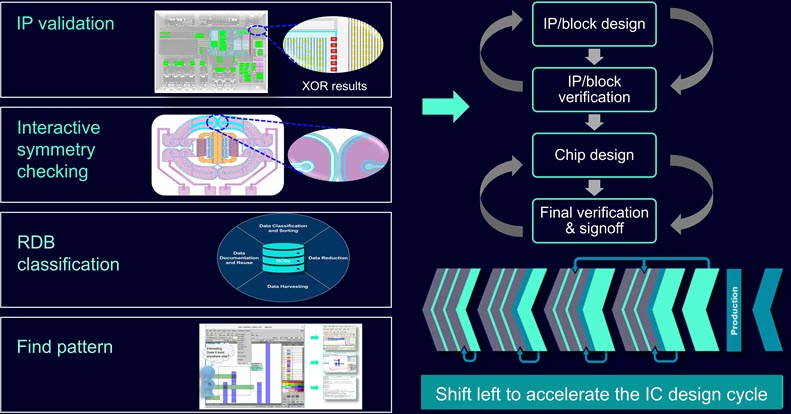

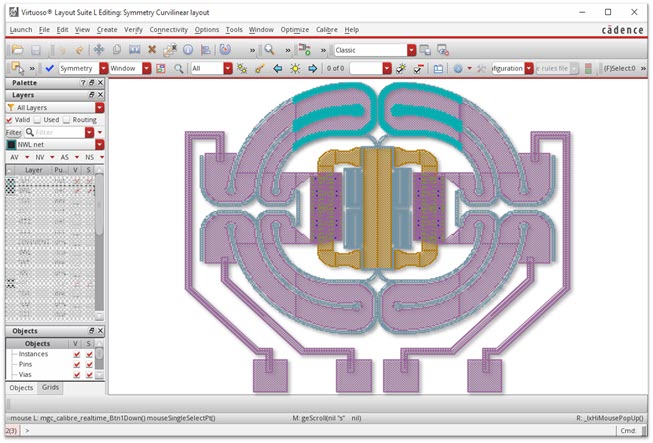

To address these challenges, a shift left approach (figure 1) to verification moves critical checks earlier in the design flow. Siemens’ Calibre Pattern Matching enables IC designers to verify IP placement, confirm symmetry, and debug issues interactively—without the need for rule coding. This proactive approach seamlessly integrates into existing design flows to reduce design iterations and accelerate time to tape-out.

The growing complexity of IC verification

Many conventional verification methods rely on manual measurements and custom rule-based design rule checks (DRCs), which are often performed late in the design process. These methods introduce several challenges:

- Late detection of errors: Initial development of custom rules to verify an IP layout is not modified implies the rules are created based on the completed IP, meaning when the IP is complete.

- Expertise and maintainability: Design changes for device optimization or any reason means changing the rules accordingly. This rule expertise adds to the complexity of maintaining those rules as IPs evolve and rule coders move on.

- Reliance on an “honor system”: IP providers are expected to deliver foundry-clean layouts, but end customers bear the responsibility of verifying placement accuracy and compliance with manufacturability standards.

Why symmetry checking matters in analog/mixed-signal IC design

Symmetry is essential in analog and mixed-signal designs to ensure optimal circuit performance and reliability. However, symmetry checking is often deferred due to its time-consuming nature. Manual methods, such as measurement tools and cell mirroring, introduce a risk of human error, and even correct-by-construction techniques can provide a false sense of accuracy if not properly validated.

Delaying symmetry verification increases the likelihood of discovering issues late in the design cycle, leading to multiple iterations and production delays. The need for an efficient, automated symmetry checking solution has never been greater.

A smarter approach to IC verification with Calibre Pattern Matching

Calibre Pattern Matching provides a pattern-based approach to early-stage verification, allowing engineers to catch and resolve potential issues before they become costly problems. Here’s how it enhances the IC design workflow:

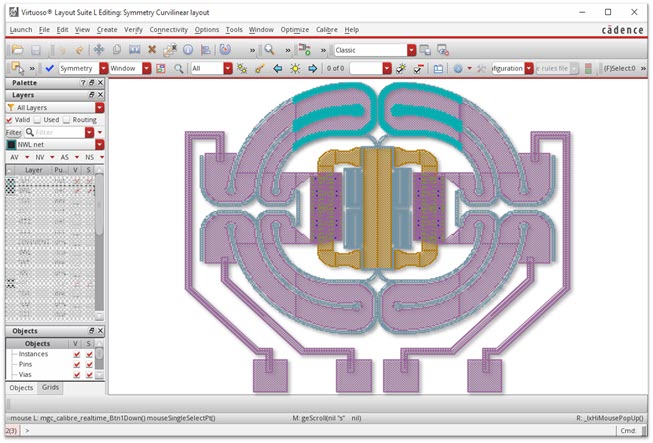

1. Interactive symmetry checking with Calibre RealTime

With Calibre RealTime, engineers can verify symmetry at any stage of the layout design cycle. This push-button verification occurs directly within the design environment, eliminating the need for specialized rule coding or manual measurements. Benefits include:

- Immediate detection of symmetry violations

- Precise XOR differences for easy symmetry debugging

- Continuous assessment as the design evolves

2. Pattern-based IP Verification

Calibre Pattern Matching also simplifies IP placement and alignment verification. Instead of relying on text-based rule coding, engineers can:

- Verify the presence and placement of IP blocks early in the design

- Identify misalignment issues quickly

- Ensure that IP blocks remain unchanged throughout the design process

This approach ensures that IP integrity is maintained, reducing the risk of functional errors and layout mismatches.

3. Push-button inline pattern search

Identifying layout configurations has traditionally required extensive rule coding expertise. With Calibre’s “Find Pattern” feature, engineers can now locate patterns within a layout using a simple point-and-click interface. This feature enables:

- Fast identification of problematic layout patterns

- Simplified failure analysis and debugging

- Zero-code pattern search, making verification more accessible

Case study: Early detection of symmetry and IP placement issues

A leading semiconductor company specializing in CMOS audio controllers faced unexpected audio distortion due to unidentified asymmetry in an amplifier circuit. Their traditional symmetry checking method failed to detect the issue, leading to reliability issues throughout the product’s life. By integrating Calibre Pattern Matching, the company was able to identify symmetry violations in real-time, preventing late-stage design revisions. Additionally, they enhanced IP placement verification, ensuring accurate alignment and reducing functional errors. As a result, the company achieved faster time to tape-out, improved verification efficiency, and a higher-quality final product.

Maximizing IC design efficiency: Key benefits of Calibre Pattern Matching

By adopting shift-left verification with Calibre, IC design teams can:

- Detect symmetry issues early: Reduce rework by validating symmetry in real-time.

- Improve IP placement accuracy: Ensure that all IP blocks are correctly positioned from the start.

- Enhance debugging efficiency: Prioritize and resolve critical verification errors faster.

- Reduce overall design iterations: Catch and correct issues before they escalate.

- Accelerate time to market: Minimize delays and improve design quality.

Conclusion: A modern approach to IC Verification

IC designs are more complex than ever, and traditional verification methods are struggling to keep pace. By leveraging Calibre Pattern Matching and Calibre RealTime Digital and Calibre RealTime Custom, designers can verify layouts interactively, detect symmetry issues early, and ensure accurate IP placement—all without the need for complex rule coding.

The shift-left methodology represents the future of IC verification. With real-time, pattern-based verification integrated directly into the design flow, engineers can confidently address layout issues as they arise, reducing design iterations and accelerating time-to-market.

In an industry where every iteration impacts production timelines, early and efficient verification is a key to success.

Bonus! We have lots more content on this topic if interested – watch this short video Calibre productivity and reliability enhancement solutions or really take a deep dive with our recent technical paper Shift Left with Calibre Pattern Matching: Trust in design practices but verify early and frequently