The secret superpower of early design verification

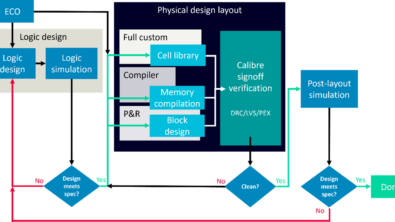

How many times, as you traversed across design stages and ran countless iterations, have you wished that you had a superpower to let you accomplish 100 things at the same time? Oh, and maybe a magic wand, so you could find and fix just actionable errors without even debugging? Unfortunately, superpowers and magic wands are pretty hard to come by in integrated circuit (IC) design, but with Calibre nmLVS Recon early design layout vs. schematic (LVS) checking, Siemens EDA can get you pretty darn close!

With the increasing complexity in ICs, companies are experiencing significant growth in circuit verification time and effort node over node. That growth, in combination with today’s tapeout-time sensitivities, makes it critical to begin checking for and fixing design issues at an early stage. The problem? In those stages, there are typically thousands, if not millions, of layout errors, only some of which are actionable. Addressing all of these errors is a prohibitive and unproductive drain on both time and resources, as many will simply disappear as the design comes together. No wonder the statistics in industry conference surveys show that 50% of tape-outs slip each year!

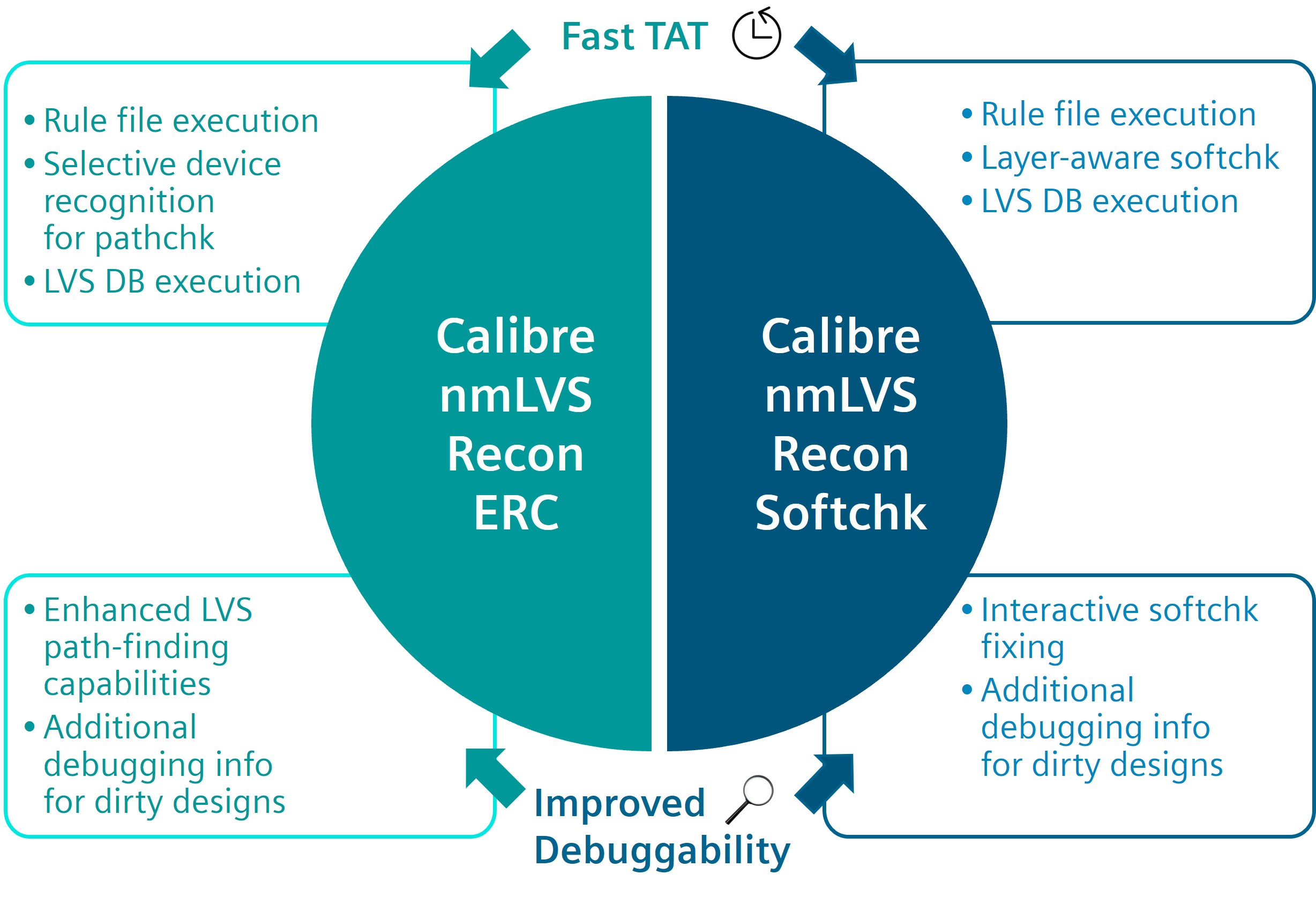

That’s when the Calibre nmLVS Recon tool comes to the rescue! As the first circuit verification tool specifically designed to improve early stage LVS verification and debugging flows, the Calibre nmLVS Recon tool helps design teams reduce overall IC design verification and debugging time while improving design quality. The tool currently provides shorts, electrical rule checking (ERC) and soft connection checking.

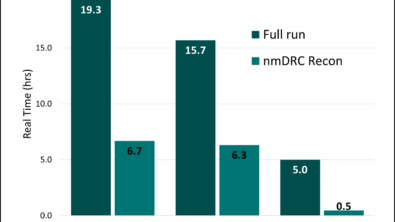

Two of the main pain points in early-stage circuit verification are ERC and soft connection checking, primarily because debugging these errors in the early design stage using a signoff flow is cumbersome, requiring a significant number of iterations and many manual steps. For example, a designer might need to wait for hours (or maybe more) for a signoff run on a dirty design just to check the results of a 5-minute check. Imagine if the check must be run multiple times? Can you relate?

The Calibre nmLVS Recon ERC and soft connection checks help designers focus only on what is relevant in early design stages, saving the time spent running unnecessary operations, and offering new capabilities for faster and easier debugging. As a result, designers can increase their productivity while improving time to market!

Want to know how you can achieve similar results? Download a copy of our technical paper, Achieve dramatic productivity and turnaround time improvements in early design electrical rule checking, and start experiencing the benefits of Calibre verification accuracy during early design stages, as well as a more confident and relaxed tapeout schedule. In our industry, that’s a real superpower!