Ease on down the road…why “ease of use” is the next big thing in EDA, and how we get there

Ease of use is an important issue when enhancing product functionality and introducing new technology. Calibre Design Systems considers ease of use a critical design factor, which is reflected in the multiple strategies and technologies we use to implement and improve ease of use throughout the Calibre nmPlatform.

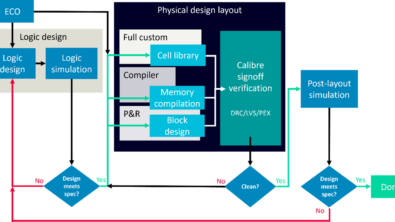

Electronic design automation (EDA) is all about simplifying and automating the process of ensuring your IC design can be turned into working silicon that delivers the performance and product life the market expects. EDA tools and technology are the crucial foundation of the semiconductor industry’s advances over the years. Moore’s law, as well as innovations like finFETs, multi-patterning, and 3D ICs, wouldn’t even be possible without the automation of the analysis, optimization, and verification processes that must happen to create the “design to silicon” flow.

But just automating a process doesn’t necessarily make it easier to use. Oh, it might speed things up, compared to visual design inspections and tedious manual layout corrections, but ease of use is as much a deliberate design goal as speed and accuracy. The team behind the Calibre nmPlatform includes ease of use as one of the critical criteria when considering ways to enhance and expand our portfolio of industry-leading verification solutions. We also recognize that ease of use is an iterative and progressive process that evolves as the tools and processes change.

Okay, but what does ease of use mean to the designers and engineers who use Calibre tools? Well, that’s the whole idea—looking at functionality from the user’s perspective, and thinking about what really makes a difference to design teams during their IC design and verification flows. It means talking to those teams, getting their insights and needs and “wish lists,” and taking all of that feedback into consideration when evaluating our platform and the individual tools.

For example, the design rule checking (DRC) process is a major percentage of the design verification flow. But, without DRC compliance, designs cannot be taped out and sent to the foundry for manufacturing. To minimize the impact of DRC batch runs on the schedule and resources of a design team, we constantly improve processing speed and memory resource use across design styles and process nodes. We also provide complementary functionality, such as pattern matching, automated waiver processing, and multi-patterning verification, that support and streamline complex DRC. And of course, ensuring Calibre performs and scales as well in the cloud as it does onsite helps companies acquire the necessary resources when physical investment on premise simply isn’t an option.

But a Calibre nmDRC batch run is still always going to require a significant chunk of time and compute resources in a verification flow, no matter how fast and efficiently it runs. So we examined the entire DRC process, and asked, “What if designers could eliminate some errors earlier in the design flow?” That train of thought led to the introduction of several innovative tools that provide design teams with early design exploration and verification functionality that accelerates DRC closure, reduces the overall schedule, and provides designers more time to focus on meeting power, performance, and area goals.

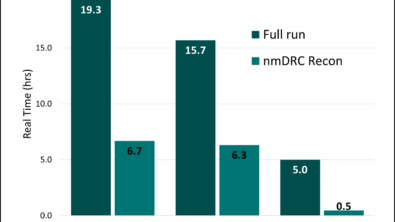

The Calibre nmDRC Recon tool provides SoC designers with the ability to run selective full-chip verification early in the design implementation and integration stages, helping them find and correct systemic errors, like off-grid block placements or routing violations, with faster runtimes and simpler debug. Minimizing full DRC batch runs early in the design cycle can add up to significant savings in overall schedule time.

Meanwhile, the Calibre RealTime Custom and Calibre RealTime Analog tools enable on-demand Calibre signoff DRC within the design and implementation environments, allowing designers to perform targeted DRC checks on the layouts and receive immediate Calibre DRC feedback. With that information, they can quickly apply and verify fixes with Calibre confidence that the results are DRC-clean.

Those are just a couple of examples focusing on the DRC flow, but the same attention is paid to every part of the design verification and optimization flow, and to every tool in the Calibre portfolio. Constant optimization and innovation are key to improvements in ease of use.

Ease of use isn’t just about performance, though—it’s also connected with how easy and intuitive it is to use a tool. Developing and enhancing tool GUIs to provide quick selection of check and run options and requirements lets designers focus on the task at hand, rather than spending time writing code. And, because Calibre tools are integrated with a wide variety of design and implementation environments, we strive to ensure consistent interfaces across all integrations so design teams can easily switch between different tools as needed.

Interested in learning more about how Calibre Design Solutions constantly looks for ways to improve ease of use for the Calibre nmPlatform? Here are some links you might like to explore…

Visiting our product pages is a great place to start! You can browse the entire range of Calibre Design software solutions, or hone in on a particular topic by browsing the resource library link at the top of each product family page.

If you want to get right to the nitty-gritty details, here are some recommended resources discussing how the Calibre nmPlatform is providing an improved ease of use experience in the physical verification flow:

Technical papers:

Automated post-processing of DRC errors improves debugging productivity

Data integrity checks save time and resources in parallel IC design flows

Custom integrity checks find early IC design implementation errors

Advanced symmetry checking in IC layout design and verification

Construct by correction with selective verification enhances productivity

EDA in the cloud—Now more than ever

Videos:

Calibre physical verification – Solutions for your next node

Accelerate PV closure using Calibre RealTime Digital DRC

Enhanced P&R designer productivity and design quality Calibre RealTime platform overview