Do you trust the reliability of your 2.5D/3D IC package designs?

By Dina Medhat

2.5D/3D ICs have become an innovative solution for many design and integration challenges. Basic physical verification for 2.5D/3D IC layouts is well covered by EDA solutions currently available in the technology market, with the main focus on DRC and LVS checks, including physical alignment checking (e.g., scaling, orientation, bumps overlap, separation distance) and connectivity checking. But what about advanced verification challenges, such as electrostatic discharge (ESD) robustness, advanced latch-up design rule checking, candidate hot junction detection, and more. How do you address these reliability concerns in multi-die packages?

To begin with, designers need to understand some critical differences between 2D ICs (single die packages) and 2.5/3D ICs. From a reliability verification perspective, 2.5D/3D ICs are not just a group of independent 2D ICs connected together. For example, ESD protection devices can span multiple dies, and must be combined for correct evaluation. Applying the correct type and amount of reliability verification to 2.5/3D ICs begins with recognizing how these differences impact the susceptibility of an IC package to typical reliability threats.

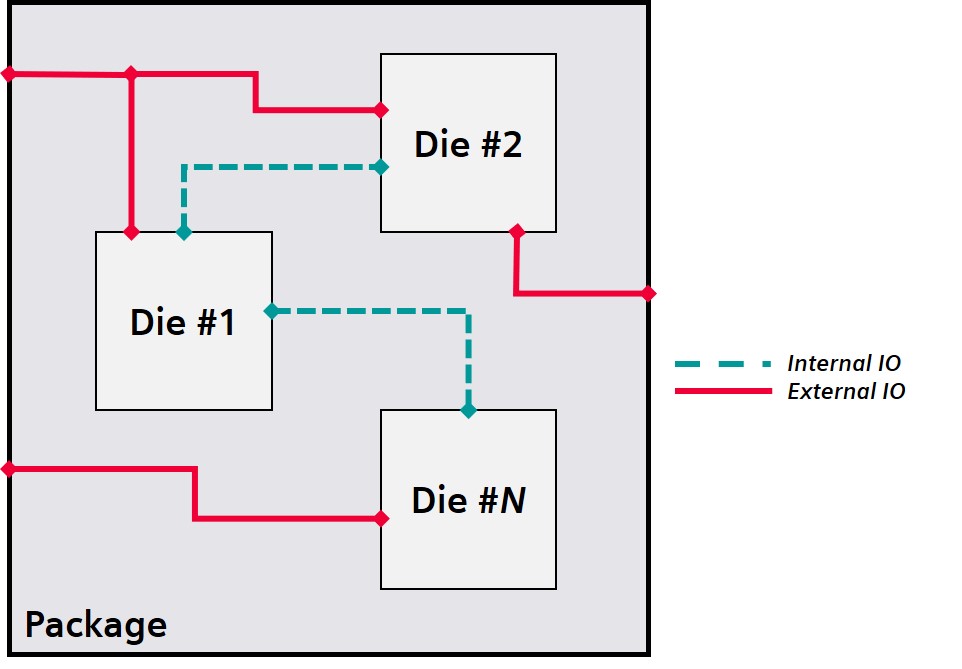

In 2D ICs, almost all IC pads, if not all, are connected to the outside world through the package pins. With multiple dies in 2.5D and 3D integrations, some pads only connect signals between dies through micro-bumps, TSVs, and the interposer, and do not connect with the outside world at all. This key difference in 2.5D/3D IC layouts requires designers to differentiate between those two categories of pads by classifying them as external IOs (connect to the outside world) or internal IOs (no external connection). Such classification is essential because external IOs are connected to the package pins, which means they will face significantly more ESD events than internal IOs. Similar to traditional 2D ICs, external connections with IOs are affected by both human body model (HBM) and charged device model (CDM) ESD events. However, internally-connected IOs will be considerably less exposed to HBM and CDM events. This difference in potential exposure directly translates into smaller ESD protection circuits being needed for internal IOs, which in turn saves die area and cost, without sacrificing any ESD protection robustness for the complete package.

The difference in ESD protection requirements isn’t the only dissimilarity between internal and external IOs. Internal IOs also have low latch-up risk, so designers can simply skip latch-up detection for these pads. Moreover, there are no hot junctions based on internal IOs, so designers can exclude internal IOs when searching for candidate hot junctions.

Of course, trying to manually identify and label all IOs in a package design is not only time-consuming, but susceptible to human error. At Siemens EDA, we implemented systematic methodologies using the Calibre PERC reliability platform to help designers overcome these reliability verification challenges in 2.5D/3D ICs. Differentiation between external IOs and internal IOs can be performed quickly and automatically from the assembly level, without the use of any special layout markers on the die level, eliminating the chance of human error. Advanced latch-up DRC and candidate hot junctions detection are performed on external IOs only. A topology-aware flow is used in conjunction with external latch-up design rules, while a voltage-aware flow is used for mixed-voltage latch-up design rules. Implementing an automated reliability verification solution for 2.5D/3D IC designs ensures accurate and consistent protection, regardless of the type or complexity of the package.

Interested in learning how your company can begin improving the reliability of its 2.5/3D IC designs? Download a copy of our technical paper, Reliability verification in 3D IC designs, and explore how automated reliability verification can help you create efficient, robust package layouts that deliver the performance and product life required by today’s demanding markets.