Tessent wins Best Paper award at IEEE VLSI Test Symposium

The best paper of the 2020 symposium describes a layout-friendly EDT decompressor that reduces routing congestion associated with decompressor circuitry

Tessent authors Yu Huang, Janusz Rajski, Mark Kassab, Nilanjan Mukherjee, and Jeff Mayer earned the VTS Best Paper award for their 2020 submission “Effective Design of Layout-Friendly EDT Decompressor.” The award was announced during the VTS 2021 plenary session.

The paper describes an innovative layout-friendly decompressor design used in the Tessent EDT (embedded deterministic test) architecture on which Tessent TestKompress operates. The new decompressor design is proven on several large industrial designs to significantly reduce the routing congestion associated with the decompressor circuitry compared to traditional approaches. This makes it easier to use Tessent TestKompress with very high compression ratios on large, complex designs.

Tessent layout-friendly EDT decompressor

In the context of testing a modern SoC design, scan test compression technologies are necessary for controlling the overall cost of test. The compression hardware is logic embedded on a chip, inserted along the scan path but outside of the design core. It normally consists of two main blocks: 1) a decompressor that feeds the test stimuli to many internal scan chains from a few scan channels, and 2) one or multiple on-chip compactors that compact the test responses from the internal scan chains to the scan channel outputs.

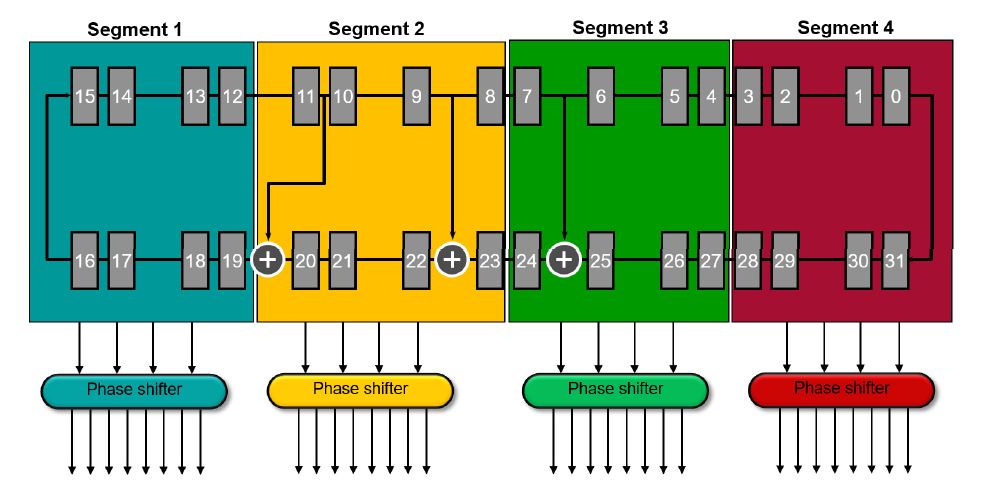

The compactors can be associated with just a subset of chains so they don’t cause routing congestion. But, the decompressor can cause significant routing congestion because it can drive thousands or tens of thousands of internal scan chains. Given that compression logic is often insert at the RTL when no layout information is available, mitigating the congestion impact has been a challenge. The solution created by the Tessent engineers is a segmented decompressor that is inserted at RTL and reduces congestion in the layout. The decompressor is partitioned into multiple segments, each driving only one subset of internal scan chains. The inputs of XORs in the phase shifter of one segment are connected to taps within this segment only. This reduces the routing congestion because you can distribute decompressor segments within the layout to avoid the routing hot spots.

The details, of course, are beyond the scope of this blog. But, you can watch Janusz Rajski’s presentation of the VTS paper here.

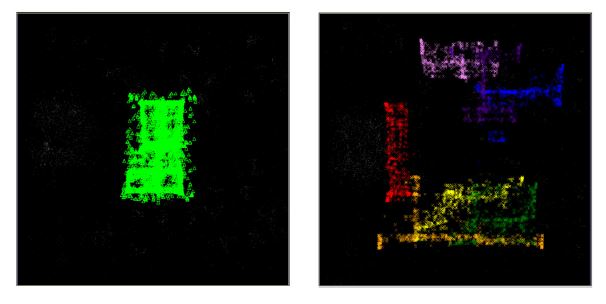

The layout-friendly segmented decompressor technology was tested on nine large industrial designs. The results show almost identical test coverage and an average of 5% smaller pattern count compared to a centralized decompressor. The new decompressor has 1.91X reduction on the overcongested edges, and 1.35X reduction on the worst overcongestion number. The following image compares the layout routing for a single, central decompressor (left) to the new segmented decompressor.

The Tessent R&D group, part of Siemens Digital Industries Software, is dedicated to innovation in IC test that advances the success of our customers and partners. Recognition from the DFT community is solid validation that we are serving the needs of the industry as it tackles the thorny issues of large and complex designs, tight development schedules, and cost pressures.