New innovative way to functionally verify heterogeneous 2D/3D package connectivity

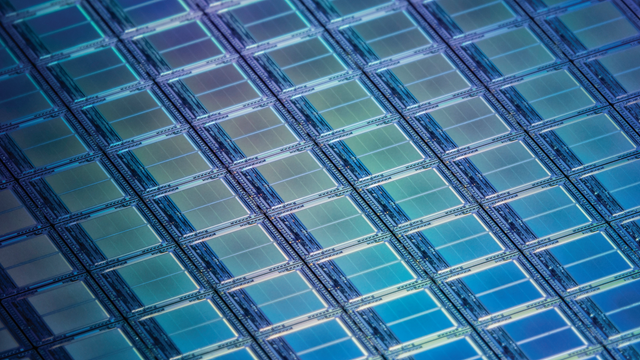

Historically, integrated circuit (IC) package design was straightforward, involving die bumps fanned out for connection to a printed circuit board. The package netlist was manually created by package designers using tools like Excel. However, modern package and interposer design is now a complex, system integration task. Designers must consider input from various stakeholders who may be concurrently designing content.

Challenges in Modern Substrate Design

The term “substrate” generically represents both package and interposer designs. Despite differences in manufacturing technology and tools, the design and verification tasks remain similar. In both cases, rapid advances in package technology and the explosion of AI and high-performance computing applications give rise to design challenges that are breaking the existing methodologies used by substrate designers. These include:

- Connectivity Complexity – Designs with 500,000 bumps and hundreds of thousands of connections already exist, and hybrid bonding technology promises millions of bump connections. Spreadsheets are no longer sufficient for managing complex connectivity.

- Heterogeneous Integration Challenges – Source data is supplied in various formats (e.g., Ball map CSV, LEF/DEF, GDS, Verilog RTL, plain text), and each of these components must be connected to others in the system, even those having different formats.

- Language-Based Design Solutions – Although Verilog RTL with proper bus notations is more efficient, spreadsheet-based solutions don’t scale for large designs.

Standard Functional Verification Is Not Enough

The appeal of functional verification is that it validates correct system connectivity and functionality and appears solvable due to in-house chip design. However, additional information is required beyond the main silicon device, such as:

- Functional models for each die

- Models for discrete components

- Testbenches for verification

Challenges with Chiplets

Chiplets, such as those for high-bandwidth memory (HBM), frequently lack functional models. Substrate designers face challenges due to limited access to chip RTL and verification environments, while expertise is required to adopt and execute verification tools.

Skillset Gap

Developing specialized Verilog models and testbenches is not typically within the domain of package and interposer designers.

Practicality

Technically possible but often impractical due to resource constraints.

What About LVS? (layout versus schematic)

LVS checks whether the physical implementation (layout) corresponds to the original schematic or circuit diagram of the design. It ensures that the devices and nets in the layout match those in the schematic. However, LVS alone doesn’t guarantee functional correctness. It focuses on netlist consistency but does not assess functionality.

If the layout matches the source netlist, LVS considers the comparison “clean.” However, this approach assumes that the source netlist is accurate. If the source netlist contains errors or is incomplete, LVS may still “pass” even if the design is functionally flawed. The layout may match an incorrect netlist in such cases, leading to a false sense of security.

In short, LVS can identify physical discrepancies (e.g., shorts, opens) between the layout and schematic. But it cannot determine if the design functions correctly, assess whether the design performs its intended function, nor address questions related to design correctness. Designers must consider additional verification methods beyond LVS to ensure overall correctness.

Automatic Formal-Based Approach

Formal verification tools are suitable for verifying package connections early in the design process. These tools focus on connectivity checks without requiring extensive testbenches or assertions. And unlike simulation-based approaches, formal connectivity solutions don’t necessitate understanding the design’s functionality.

The benefits and considerations related to formal verification for verifying package connections in chiplets include:

- Detecting connection errors

- Ensuring correctness of connections

- Avoiding short circuits

- Handling complex systems

- Detecting flaws early

- Assuring safety and reliability

- Validating compliance

As a bonus, when verifying package connections after prototyping, companies can use existing CSV specs or create new ones. The system top module and black boxes of the dies serve as the golden reference model for verification.

Get the white paper

To learn more about modern package and interposer design, download this white paper entitled: “New innovative way to functionally verify heterogeneous 2D/3D package connectivity.“

This paper authored by Michael Walsh and Jin Hou from Siemens EDA addresses challenges related to verifying package connectivity and demonstrates how setting up and running the formal tools is straightforward, requiring only a few minutes and how connection extraction and package connection verification are fast, even for large systems with multiple dies. The methodology minimizes manual work, and once set up for one design, it can be easily reused for others with minimal adjustments. It also shows how starting connectivity verification early using formal methods significantly improves the quality of physical implementation and shortens the time to market and how the user-friendly nature of this approach encourages adoption with immediate benefits.

Want to learn more about 3D IC technology?

- Listen to The future of semiconductor design podcast, in which industry experts discuss 3D IC concepts and the latest trends: chiplet designs, IC packaging, multi-die verification, golden netlists, electrical signoff, system analysis, and more!

- Read The beginner’s guide to 3D IC to discover how 3D IC is evolving.

- View this infographic to learn how to Unlock the potential of 3D IC.

- Learn more about 3D IC front-end design planning and predictive analysis in this ebook entitled “Launching the full potential of 3D IC with front-end architectural planning”

- Discover the 3D IC design workflows available to designers in this eBook entitled: Semiconductor packaging: making the right connections in 3D IC design