Closing the Gap: How Tessent CellModelGen Elevates Semiconductor Test Accuracy

In today’s semiconductor manufacturing, the pursuit of perfection leaves no room for error. Traditional testing methodologies often miss subtle yet critical cell-level defects. Tessent’s CellModelGen tool revolutionizes this landscape by providing a fully automated, highly precise method of generating cell-aware ATPG models. By operating directly at the transistor level, it identifies potential issues that earlier methods overlooked, ensuring superior defect coverage across integrated circuit designs.

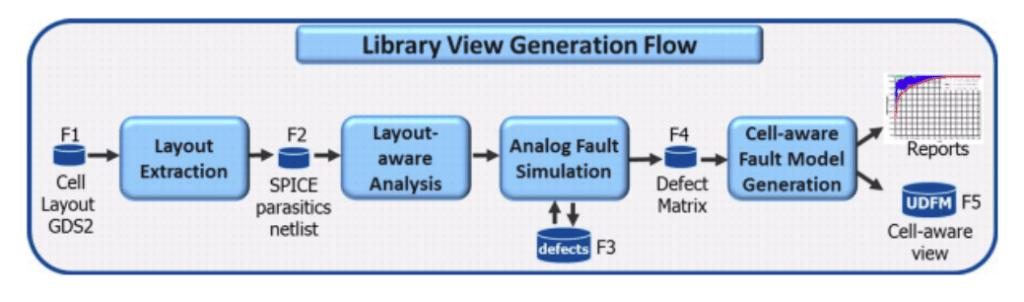

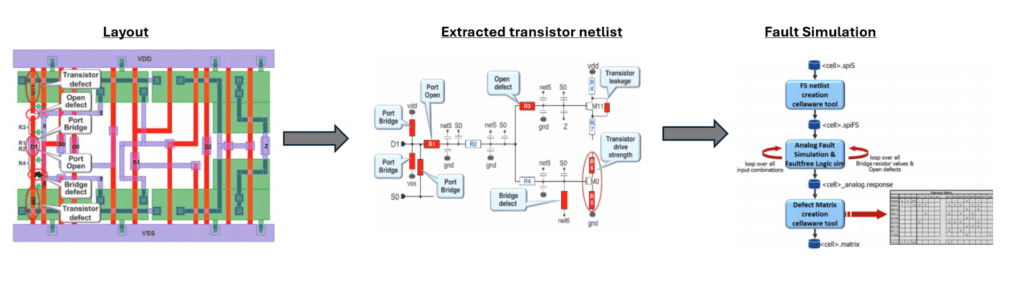

The effectiveness of Tessent CellModelGen comes from its methodical, four-step characterization flow—layout extraction, defect analysis, analog fault simulation, and finally cell synthesis. Initially, it extracts detailed transistor-level netlists along with associated parasitic elements. These extracted data sets form the basis for comprehensive defect analytics, precisely calculating critical defect probabilities and areas. Subsequently, CellModelGen runs targeted analog fault simulations to rigorously evaluate and capture every possible defect detection scenario within the library cells, enabling an optimized and accurate cell-aware library generation.

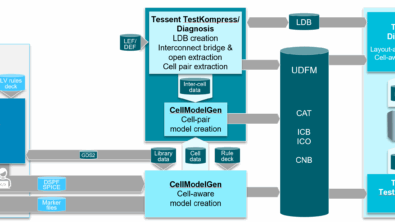

Beyond just accuracy, the tool also provides significant process flexibility. Engineers can choose to apply Tessent CellModelGen either on an individual cell basis or scale up effortlessly to an entire cell library. Its output models, provided in standardized User-Defined Fault Model (UDFM) format, integrate smoothly with Siemens’ Tessent ATPG solutions like TestKompress and FastScan. Leveraging this integrated workflow, Users can deploy highly reliable static and delay tests, ensuring superior device quality and minimized field failure rates.

Ultimately, the value of Tessent CellModelGen extends beyond initial test generation; its benefits propagate throughout the lifecycle of the semiconductor device. With the integration of Tessent Diagnosis, users achieve great diagnostic depth, quickly pinpointing the exact locations and root causes of even the most obscure cell-internal defects, including opens, bridges, and transistor-related issues. This advanced capability translates into quicker problem resolutions, continuous product improvement, and sustained competitive excellence within the semiconductor industry.

For More Information refer to the Cellmodelgen reference manual Tessent CellModelGen Tool Reference