Smarter DRC for complex designs: Accelerating verification with Calibre nmDRC Recon

By John Ferguson

The challenge: Traditional DRC can’t keep up… Increasing complexity and automation in IC design have made traditional design rule checking (DRC) methods less effective. Originally built for simpler, manual layouts, legacy DRC workflows follow a “construct by correction” method—running checks after layout completion, flagging violations, and then iterating fixes. While this worked in the past, today’s designs are multi-layered, hierarchical, and often developed by distributed teams, making full-layout DRC verification a major bottleneck.

Why does traditional DRC struggle?

- Long runtimes – As design rules grow in complexity, verification runtimes increase exponentially.

- Incomplete layouts – Many designs are finalized in stages, making full verification impractical until later in the design process.

- Debug inefficiencies – Global rule violations take longer to trace and correct due to their non-localized nature.

The impact? Teams face significant delays in debugging and validation, often leading to extended tape-out timelines and increased resource consumption.

The solution: A Shift left approach with Calibre nmDRC Recon

Recognizing these challenges, Siemens introduced Calibre nmDRC Recon, a revolutionary shift left verification strategy designed to perform early, localized rule checks, reducing debug times and resource consumption. Instead of waiting for full-layout readiness, nmDRC Recon enables designers to catch and correct major layout violations much earlier in the design cycle.

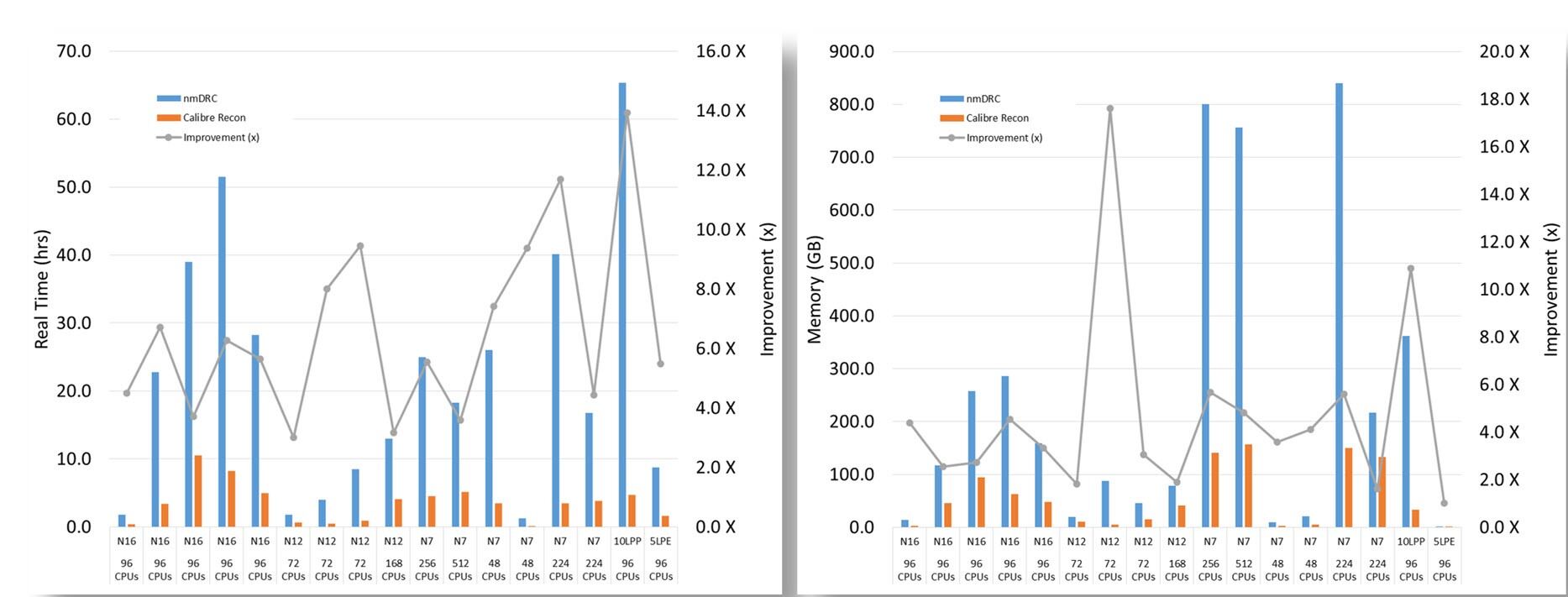

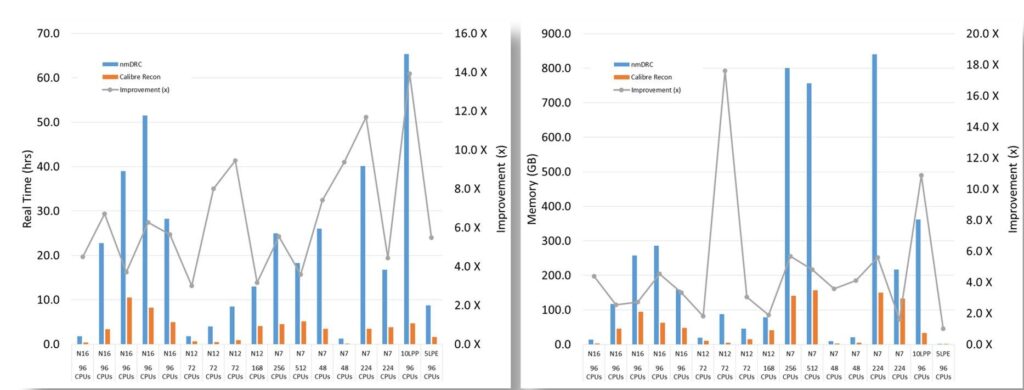

One of the key advantages of nmDRC Recon is its ability to accelerate debug cycles. By running only relevant, local-scope checks, it significantly speeds up the verification process, allowing designers to identify and address errors more efficiently.

Another major benefit is the reduction in compute load. Instead of processing an entire design at once, nmDRC Recon selectively verifies specific design components, which helps minimize hardware requirements. This makes it a practical solution for teams working with limited computing resources.

Finally, nmDRC Recon enhances targeted error detection by pinpointing violations closer to their root cause. This minimizes unnecessary iterations and helps designers focus on resolving key issues without being overwhelmed by unrelated errors. The result is a more streamlined and efficient verification process that ultimately accelerates time to tape-out.

How Calibre nmDRC Recon streamlines and accelerates DRC verification

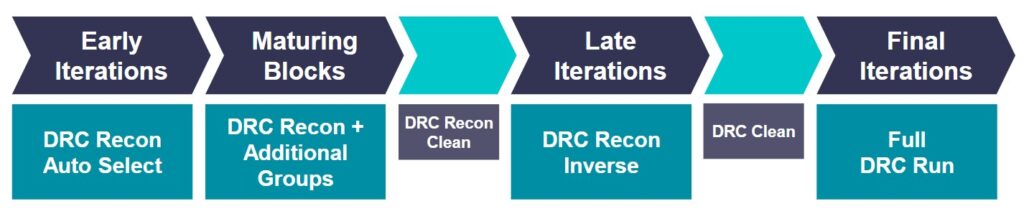

Calibre nmDRC Recon focuses on local verification first, meaning it runs checks that don’t require deep hierarchical analysis or connectivity data. This reduces runtime and hardware usage significantly. Here’s how designers can leverage it:

1. Early-stage verification with localized checks

Traditional DRC runs all rules across the full layout, even when only partial data is available. Instead, nmDRC Recon focuses on local scope violations—those not dependent on hierarchy or connectivity. This enables early detection of gross errors in:

- Floorplanning

- Cell placement

- Chip finishing

By resolving these issues sooner, designers avoid compounded errors later in the flow.

2. Customizable rule selection

Not all DRC rules are equal in complexity. With Calibre nmDRC Recon, teams can modify default behavior by enabling or disabling specific rule types. For example:

- Designers can run onlychecks related to modified layers, focusing debugging efforts on recent changes.

- Certain checks can be prioritized or deferred, allowing designers to balance speed and thoroughness.

This flexibility ensures that teams only run the rules that matter at each design stage.

3. Accelerating full verification with connectivity-aware checks

Even after resolving local violations, some checks—such as electrostatic discharge (ESD), latch-up, and multi-patterning rules—require full connectivity data. This is where Calibre nmLVS Recon SI comes in (quick video available here! Watch: Calibre nmLVS Recon)

By performing fast connectivity analysis and pinpointing shorted nets early, Calibre nmLVS Recon SI prevents unnecessary DRC slowdowns and debug cycles, ensuring that later iterations are efficient and meaningful.

Real-world impact of Calibre nmDRC Recon

One of our customers was facing significant DRC verification bottlenecks in their IC designs, adopted Calibre nmDRC Recon to enhance productivity. Their approach:

- Integrated nmDRC Recon at the floorplan and physical implementation stages.

- Focused on early detection of power-ground shorts.

- Achieved significant runtime reductions compared to traditional methods.

You can read more about Calibre nmDRC Recon in our recent technical paper now available The power of shift-left DRC verification with Calibre nmDRC Recon

The future of IC design verification

With nmDRC Recon and its associated tools, IC design teams can dramatically reduce verification runtimes, improve debugging efficiency, and accelerate time-to-market. The shift-left approach isn’t just a trend—it’s a necessity for modern, high-complexity designs.

For designers facing increasing pressure to optimize their workflows, tools like Calibre nmDRC Recon and nmLVS Recon SI provide a scalable, intelligent, and resource-efficient solution to the challenges of traditional DRC.