Transistor-level EMIR analysis from custom design tools? It’s all about flexibility!

By Roger Kang

How do you run transistor-level electromigration and voltage drop (EMIR) analysis—command line or an interactive invocation GUI? Does your layout designer have to wait for circuit designers to provide EMIR results and guidance before fixing any violations, and then iterate over and over until all EMIR violations are fixed? Maybe you’d prefer a new approach? How about one that lets layout designers deliver a high quality layout with no design rule checking (DRC), layout vs. schematic (LVS), or EMIR violations, and then enables circuit designers to use the same EMIR analysis settings as the layout designers to perform a final check with new simulation results before tapeout?

Most analog circuit designers receive the DRC/LVS clean GDSII file from the layout designer, then run parasitic extraction, followed by EMIR analysis and debug. They analyze the EMIR issues, work with the layout designer to debug and fix all EMIR issues, then re-run circuit simulation and EMIR analysis on the new layout to confirm the fixes.

However, this approach can result in long turnaround times, especially if the circuit designer and layout designer are in different time zones. A dedicated integration flow that can run DRC/LVS/EMIR applications within the custom design tool can enable both layout designers and circuit designers to use the same settings to run EMIR analysis, debug violations using the same user-friendly GUI, and cross-probe highlight violations to design tool.

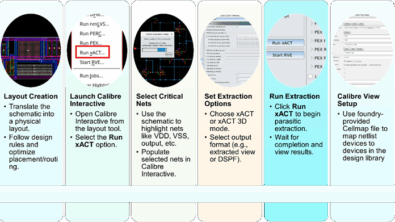

Calibre Interactive

The Calibre Interactive invocation GUI enables layout designers to extend traditional DRC/LVS/PEX flows to run EMIR analysis and fix the worst IR drop and EM violations with less circuit designer involvement. Circuit designers can then use the same settings to run EMIR analysis with new simulation results and tape out with fewer iterations without involving layout designers as much.

Additional resources for EMIR

Interested in learning more? Check out these resources:

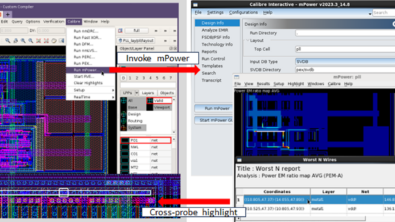

Flexible transistor-level EMIR analysis for analog/custom IC designs explains how designers can use the Calibre Interactive interface to run mPower Analog EMIR analysis in their preferred design environment and cross-probe highlight violations.

Setup and Run mPower Analog EMIR Analysis from Calibre Interactive GUI provides a brief video demo of the setup and invocation process.