Give me my space! Why high voltage and multiple power domain designs need automated context-aware spacing checks

By Sherif Hany and Abdellah Bakhali

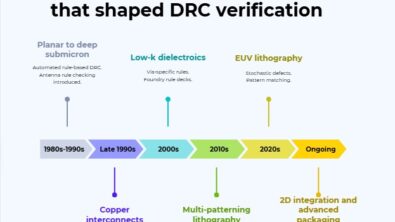

Regardless of which technology node they’re using, design houses that create high-voltage and multiple power domain designs need exacting accuracy to achieve the high reliability and high yield that contributes to the market success of these products. As they advance from one node to the next, that level of precision gets harder to achieve—the complexity of spacing checks in today’s design rules, compounded by tightly-packed layouts in which a high-voltage net is often routed closely to a low-voltage net, are making it tougher and tougher to comply with all the process, reliability, and power management requirements and still get to market on schedule. Time to ensure these designs get just the space they need, without crowding the tapeout schedule…

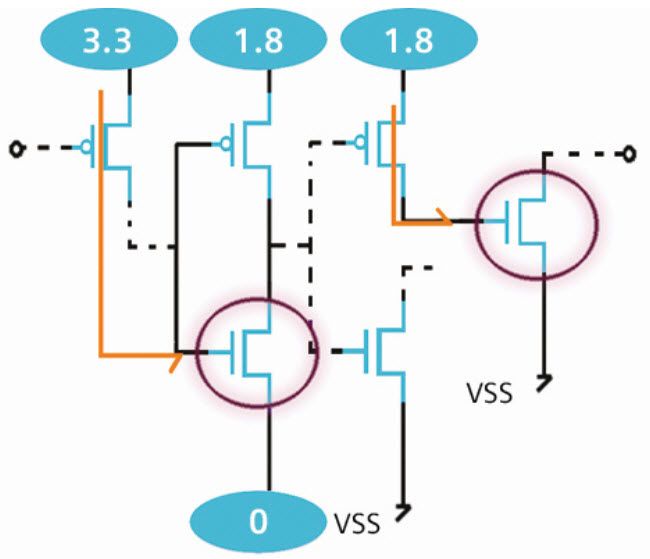

Voltage-aware design rule spacing checks (VA-DRC) are one example of “context-aware” checks that require both electrical and physical information—in this case to determine the correct (required) spacing between polygons based on voltage values. However, implementing these types of checks without automated assistance typically means using error-prone manual net annotation to mark your layout. Even worse, once you get the results, there is little guidance to help you debug and fix geometric violations that include an electrical component. Traditional EDA tools just weren’t designed to cross the boundary between physical and electrical verification.

However, the growth in advanced node high-voltage and multiple power domain applications that require high reliability, such as power management and automotive electronics, has driven both the need for these types of checks and automated, context-aware verification flows that can provide the accuracy, precision, and reliability these checks demand, while also supporting timely tapeout and successful manufacture of the designs.

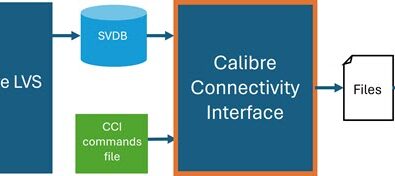

By leveraging the power of both the Calibre nmDRC and Calibre PERC platforms, the Calibre nmPlatform enables designers to perform automated context-aware voltage propagation and annotation for the voltage domains of each polygon/net, and determine the correct geometric spacing based on the absolute or delta voltages of those nets. Automated context-aware checking also enhances output results by associating the net voltage domain information to the spacing violations, providing actionable feedback (including the electrical component) to assist the designer in the debugging and fixing phases. Using this automated context-aware verification flow, designers can implement VA-DRC with confidence, regardless of design complexity or process node.

To get the full details on how you can improve the accuracy of your context-aware VA-DRC checks, perform more accurate and efficient debugging, and reinforce proven reliability optimization strategies to ensure your layouts have just the right amount of space, download our white paper: Calibre PERC advanced voltage-aware DRC delivers exacting accuracy for today’s complex designs.

Now that your designs have their space, maybe you can even reclaim a little space of your own, like that comfy spot on the couch…

Oh, and stay tuned…we have more innovation coming your way soon! Want a hint? <whispering softly> How about an automated text annotation mechanism that integrates with your foundry-qualified sign-off decks?