Early circuit verification can get you to tapeout faster…here’s how

For the last few years, it’s been hard to see design teams struggling to meet tapeout schedules caused by increasing design complexity, design size, and the sheer number of devices and polygons, not to mention new types of devices, more complex verification measurements and calculations, design for manufacturing optimization, and on, and on, and on. In fact, looking at that list, it’s a wonder teams ever get to tapeout at all!

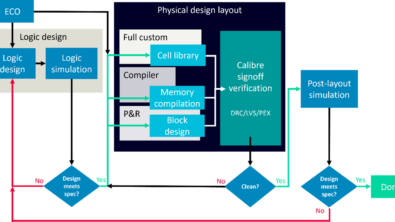

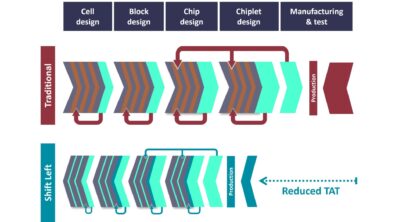

To help address these issues, Siemens EDA decided to focus on one particular pain point—the verification of full-chip design layouts during very early stages of the design cycle, while the different components are still immature and the layout still incomplete. Why early verification? A lot of systemic errors aren’t really relevant or useful in early design verification. Weeding out these errors in early design stages eliminates a LOT of unnecessary debugging time and reduces resource usage. Even better, clearing these errors out of way early on reduces the number of full-chip signoff runs needed near tapeout.

Our first early verification offering was the Calibre nmDRC Recon (short for reconnaissance) technology. With the Calibre nmDRC Recon software, designers could review designs in early stages to quickly and methodically find and fix selected design rule checking (DRC) errors in “dirty” or immature designs before having to run full-chip signoff DRC.

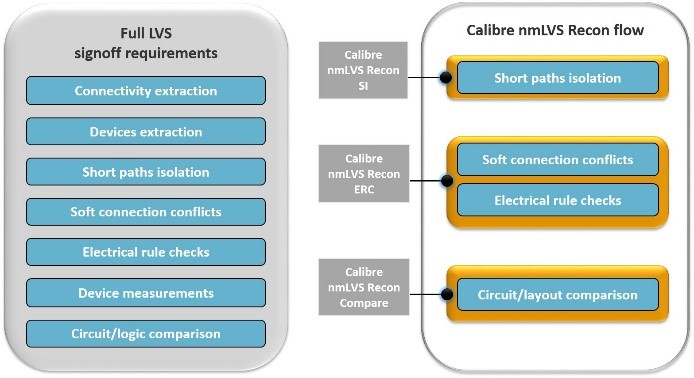

Last year, we introduced the next early verification functionality: Calibre nmLVS Recon software that will enable design teams to target specific layout vs. schematic (LVS) errors, like shorted nets, that can cause thousands of errors in early-stage designs and drive up the runtime of full LVS iterations because of their demand on hardware resources. With the Calibre nmLVS Recon technology, designers can interactively and iteratively find and fix these selected types of LVS violations before moving to full-chip signoff LVS.

Specifically, the first release of the Calibre nmLVS Recon technology is the Calibre nmLVS Recon SI functionality targeting early-stage short isolation (SI), which can take up to 80% of a design team’s early-stage verification time. 80%!!! That’s a lot of time to add back to your schedule! The Calibre nmLVS Recon SI software offers two built-in SI options—layer-aware and net-aware SI—as well as a custom SI option for teams with unique requirements.

If you’re not already using the Calibre nmLVS Recon SI technology, but you’d like to learn more, why not start with our two technical papers?

- Accelerate early design exploration & verification for faster time to market gives you a full overview of the Calibre nmLVS Recon technology, and how you can take advantage now of the SI capabilities it offers to move through early-stage circuit verification more quickly and efficiently, while reducing overall schedule time and resources.

- Increase LVS verification productivity in early design cycles delves into the details of the SI use models to explain how you can use data partitioning, focused error identification, automated selective connectivity extraction, and previously-generated databases to support task distribution and provide faster execution and smarter debug of short errors.

Early design verification is a new tool for your toolbelt that can help you achieve your design goals faster and more economically. Especially for companies targeting demanding end-markets such as the Internet of Things, artificial intelligence, autonomous driving, and 5G communications spaces, early verification can make the difference between just being in the market, and being a market leader.