Get Your Bits Together

After my last webinar on SystemVerilog arrays, I received several questions on the differences between arrays and structures, plus how to share declarations across modules. This and more will be revealed at my next webinar on SystemVerilog Structures and Packages. The first half is on structures, covering topics such as when should you pick a packed structure vs. unpacked.

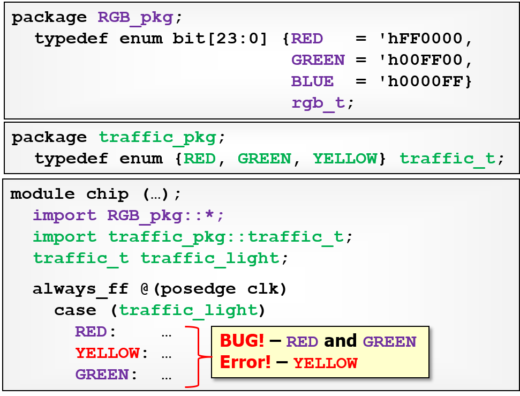

Packages are a great way to organize related definitions, like all the classes for a USB testbench, or the PCI hardware definitions. But what does it mean to import a package? In the second half of the webinar, you will learn the best place to import a package, and how to write code that avoids the problem of the same name defined in multiple packages.

For example, why won’t the following code compile compile, and what is the bug for the RED and GREEN names? Tune in and find out.

Enjoy your verification journey!

Chris Spear

Keep learning at mentor.com/training

Questions or ideas? verificationacademy.com/ask-chris-spear

View my recent webinar on SystemVerilog arrays and the Questions and Answers