Beyond simulation: Unlocking absolute certainty in hardware design with formal verification

Have you ever wondered how we can truly guarantee that the complex chips powering our world – from smartphones to self-driving cars – will always work flawlessly, even in the most obscure scenarios? It’s a question that keeps many engineers up at night, especially as designs grow exponentially more intricate.

That’s precisely the challenge addressed in my recent paper, Achieving mathematical certainty in design verification with formal. We explore how formal verification is revolutionizing hardware design by offering not just confidence, but absolute certainty in design’s correctness.

The growing chasm: Why aren’t traditional methods enough?

Modern hardware designs are engineering marvels, integrating billions of transistors, multiple processor cores, and sophisticated systems onto a single chip. Think about the System-on-Chip (SoC) in your latest device – it’s a universe of interconnected logic!

Traditionally, we’ve relied heavily on simulation to verify these designs. Simulation is powerful, allowing us to test specific scenarios and see how our hardware responds. It’s like putting a new car through thousands of test drives to catch potential issues. However, simulation is inherently probabilistic. It can only cover a fraction of all possible behaviors, limited by time and resources. This means there’s always a lingering question: what about the scenarios we didn’t test? What about that one, tiny, obscure “corner-case” bug lurking in the design?

This gap between design complexity and our ability to thoroughly verify it – often called the “verification gap” – has widened significantly. Critical bugs can slip through, leading to costly redesigns, delays, or even catastrophic failures after product deployment.

Enter formal verification: Mathematical proof, not just testing

This is where formal verification steps in as a game-changer. Unlike simulation’s “test it and see” approach, formal verification uses mathematical analysis to rigorously prove that a hardware design behaves exactly as intended, relative to its specifications. It doesn’t just test some scenarios; it systematically analyzes the complete state space of a design to guarantee correctness under all possible scenarios.

Imagine designing a microprocessor where every instruction fetch must be followed by an instruction decode. With formal verification, we write this requirement as a mathematical assertion. The verification tool then doesn’t just simulate a few hundred instruction sequences; it mathematically proves that, in all possible cases – no matter the order, timing, or combination of operations – this sequence is flawlessly maintained. This eliminates the need to simulate every single possibility, providing an unparalleled level of confidence.

For critical applications, like an automotive safety system, this distinction is paramount. While simulation might run thousands of tests, a rare combination of sensor inputs could still trigger a bug it missed. Formal verification, however, would systematically analyze all possible input sequences to ensure the safety system reacts correctly in every conceivable situation, guaranteeing the highest level of reliability.

Making the impossible possible: Smart strategies for complex designs

You might be thinking, “Analyzing all possible scenarios sounds computationally impossible for a design with billions of transistors!” And you’d be right… to a degree. The “state space explosion” problem is real – as designs grow, the number of possible states grows exponentially.

However, formal verification isn’t a one-size-fits-all hammer. My paper delves into practical strategies that make it feasible even for the most massive designs:

- Selective application: We often apply formal verification to the most critical components or properties, while simulation handles broader system-level testing. Think of verifying the core logic of a network router’s packet forwarding, while simulating its overall throughput.

- Bounded proofs: These offer a practical compromise. Instead of proving correctness for all eternity, we prove it within a specific number of clock cycles. If a digital communication protocol stabilizes within 20 cycles, a bounded proof to 50 cycles gives immense confidence without exploding computational resources.

- Abstraction: We simplify parts of the design, focusing the formal tools on the core logic relevant to the properties being checked. For a cache memory, we might verify the replacement policy on a smaller, abstract version of the cache, knowing the logic scales.

The tools of the trade: Assertions and accessibility

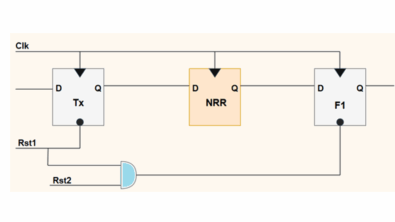

The “magic” behind formal verification largely lies in assertions. These are like mathematical contracts, specified using languages such as SystemVerilog Assertions (SVA) or Property Specification Language (PSL). They precisely define what your design must do, what inputs are valid (constraints), and what functionality needs to be exercised (cover properties).

And here’s some exciting news: formal verification is becoming more accessible than ever! While deep expertise in formal methods is invaluable for complex custom tasks, modern commercial tools offer user-friendly formal analysis capabilities. These solutions tackle specific verification challenges, allowing more engineers to leverage formal power with minimal specialized training.

Furthermore, advancements are pushing formal verification beyond traditional control logic into the realm of datapaths, which were once considered too complex due to the vast number of possible data values. My paper highlights examples like the formal verification of a 32-bit floating-point unit, proving its correctness across billions of input combinations – a feat impossible with simulation alone.

Join the journey to absolute reliability

Formal verification isn’t just about finding bugs; it’s about fundamentally changing how we approach hardware design and verification. It’s about building unparalleled trust, ensuring the highest level of reliability, and ultimately, accelerating innovation with confidence.

I invite you to dive deeper into these concepts and more by reading the full paper, Achieving mathematical certainty in design verification with formal. Discover how this powerful methodology is shaping the future of hardware design and helping us build the next generation of reliable, high-performing systems.