Pushing boundaries: Smarter verification for UCIe multi-die systems

The semiconductor industry is at a turning point. As demand for higher performance and energy efficiency continues to grow, chipmakers are moving beyond monolithic SoCs and embracing multi-die architectures. By integrating multiple dies into a single package, designers can unlock new levels of scalability, flexibility, and cost efficiency.

But this evolution doesn’t come without challenges. The dies inside these advanced systems must communicate seamlessly, and that’s where the Universal Chiplet Interconnect Express (UCIe) standard plays a central role. UCIe provides the high-bandwidth, low-latency communication fabric needed to stitch together heterogeneous chiplets into one cohesive system.

Yet, while UCIe unlocks opportunity, it also introduces complexity. Verification teams must validate interactions across multiple dies and multiple abstraction layers, making traditional block-level verification insufficient.

So how does one keep up with this growing complexity and still hit aggressive schedules? That’s where Questa™ One Avery™ UCIe Verification IP (VIP) comes in.

Why multi-die verification is harder than it looks

In traditional SoC verification, the focus is on validating isolated IP blocks. Multi-die architectures expand the problem space significantly, requiring verification of entire systems rather than individual components. The dies must communicate reliably across UCIe links while maintaining synchronization and supporting interoperability with other standards, such as PCIe, CXL, and CHI. This introduces a new layer of complexity where even minor discrepancies can ripple across multiple dies.

The challenge intensifies due to the rapid evolution of UCIe itself. Features such as the management transport protocol, lane repair, autonomous link training, and advanced sideband signalling require environments that adapt quickly to new requirements. Verification must account for both steady-state traffic patterns and rare corner cases—like failed link training or recovery from misaligned lanes—ensuring designs remain robust under all conditions.

Performance validation adds another dimension. It is not enough to check for functional correctness; verification must also track real-time system behavior, including cross-die latency, throughput, and bandwidth under realistic workloads. Subtle bottlenecks may only emerge at the system scale, making performance analysis a critical part of the verification flow.

Finally, configuration management becomes a major hurdle. Multi-die systems require synchronized register updates across all chiplets, including real-time error reporting and runtime reconfiguration. Scaling verification across platforms compounds the challenge, as teams must move from simulation with deep debug visibility, to emulation for speed, and eventually to hardware prototyping for validation under real-world conditions.

Smarter verification with Questa One Avery UCIe VIP

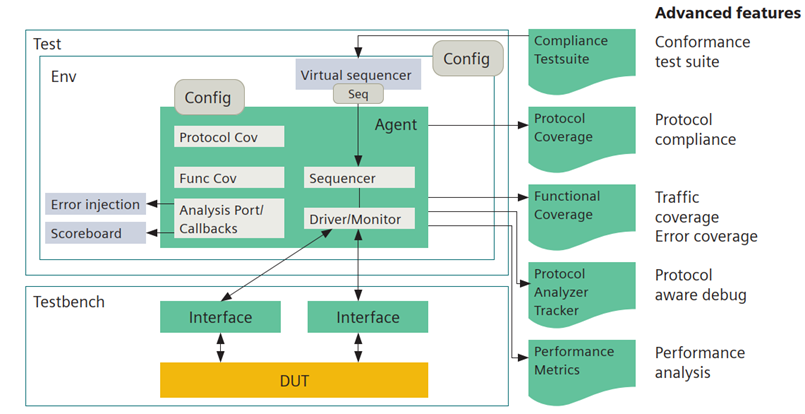

The Questa One Avery UCIe VIP addresses these challenges by delivering a flexible, protocol-aware framework that scales from block-level testing to full system verification.

Instead of weeks of manual environment set up, the Questa One VIP Configurator can generate a UVM-compliant testbench in just a few clicks, allowing verification to begin almost immediately. Its support for multiple bus functional models enables validation across LogPHY, D2D adapters, or entire die-to-die stacks, and it even supports direct RDI-to-RDI configurations for higher-level protocol testing without the physical link.

Robust controllability is built into the framework. Avery VIP supports traffic manipulation at any layer and allows fine-grained error injection, such as corrupted FLITs or invalid exchanges, to evaluate error propagation and recovery. Comprehensive test suites provide broad coverage, ranging from compliance checks tied directly to the UCIe specification to thousands of tests spanning PCIe, CXL, and CHI interactions.

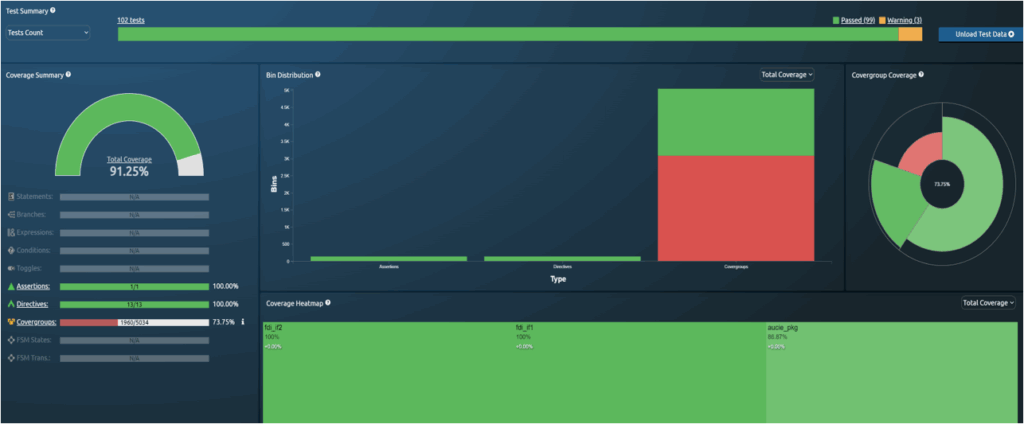

Debugging is enhanced through detailed transaction recording, finite state machine tracking, and performance loggers that capture throughput, latency, and bandwidth in real time. These capabilities make it possible to trace errors back to their source and correlate issues across multiple abstraction layers. Verification efficiency is further amplified with AI-driven coverage analysis through Questa One Verification IQ (VIQ). Acting as a co-pilot, it identifies gaps using machine learning, prioritizes tests that deliver the most coverage, and detects recurring failure signatures to accelerate closure.

Why verification matters for UCIe

As UCIe becomes the foundation for heterogeneous integration, verification is the key to unlocking its potential. It is what ensures that chiplets from different vendors interoperate seamlessly, that performance targets are met, and that reliability is maintained under demanding workloads. Without a scalable and intelligent verification strategy, the risk of hidden design flaws increases dramatically, threatening the adoption of multi-die systems.

The Questa One Avery UCIe VIP provides the automation, scalability, and intelligence needed to build this confidence. By bridging the gap between an evolving specification and the realities of silicon implementation, it enables teams to deliver multi-die systems that are production ready.

To explore the full details, download the whitepaper:

Accelerating UCIe multi-die verification with a scalable, smart framework