Video: Break through yield barriers with Siemens and PDF

At the 2023 North America User2user symposium, attendees learned about a novel approach from Siemens and PDF Solutions for speeding yield ramp and solving yield limiters through volume manufacturing.

Improving yield is key to reducing manufacturing cost and maximizing profits in a highly competitive semiconductor market. While large yield limiters are addressed early in the process during yield ramp, subtle systematic layout patterns continue to cause physical defects throughout volume production.

Thomas Zanon, an Engagement Director at PDF Solutions presented details on three key integrated solutions produced from a long partnership between PDF Solutions and Siemens Tessent group to a full room. The session was recorded and is now available for anyone to view.

In their first project together, PDF Solutions and Tessent first combined the strength of their technologies, integrating Tessent YieldInsight defect analysis with PDF’s Exensia manufacturing analytics. The outcome was a flow that accelerates time to yield by combining scan diagnosis data with manufacturing analytic to get optimized die populations and improve physical failure analysis success rates.

For their next project, they developed a new approach that extends Tesstent root cause deconvolution with layout pattern systematics to tackle layout sensitivities in products. It uses the FIRE pattern analysis engine from PDF Solutions to determine suspect groups of similar layout patterns (pattern families) and the Siemens’ Tessent RCD diagnosis-based machine learning software to produce defect Paretos. These yield Paretos include specific layout pattern families as distinct root causes and show an overall increase in defect Pareto accuracy from ~70% to ~90%. The benefit is removing the noise in random defects and layout pattern systematics and improve RCD parato accuracy.

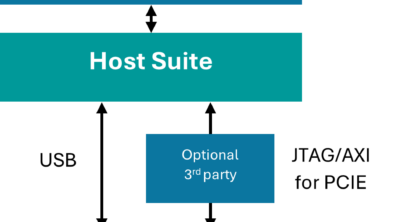

The third project focuses on accelerating analysis for complex embedded memory products. It integrates Tessent SilionInsight with the bit-mapping solution of Exensio. The Tessent portion collects fail information from memory and performs analysis of raw memory test data. Exensio is used for processing the raw memory test data and performing comprehensive memory failure analysis. The Tessent and PDF Solutions tools together provide a single efficient setup for complete embedded memory products and a comprehensive memory analysis platform.