Join Tessent at the VOICE Developer Conference

Tessent invites you to join us at the upcoming VOICE Developer Conference happening virtually from June 21-23, 2021. VOICE is a conference created by test engineers for test engineers, so is a great opportunity for gathering meaty information. Register now to reserve access to information about the latest technology advancements, new ideas, best practices, and professional networking.

Where to find Tessent at VOICE

- Our virtual booth, where you can watch a presentation, download product information and talk to experts.

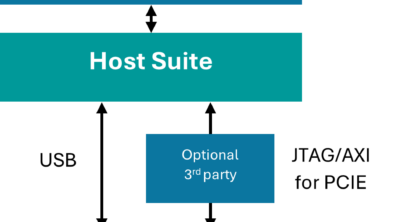

- The Technology Kiosk, where Advantest will demonstrate an IEEE1149.10 high-speed test access port and on-chip scan distribution architecture implemented on the V93000. The demo is based on Tessent’s 1149.10 scan infrastructure on an FPGA evaluation board.

- Our technical session, “Using High-Speed I/Os for Scan Test with IEEE 1149.10.” The reuse of high-speed serial I/Os for scan test will soon be essential. This paper presents a solution based on the IEEE 1149.10 standard that is usable on today’s ATE, perfectly suited for next-generation testers and well prepared to handle the enormous data volumes of tomorrow’s devices. Experimental results from an IEEE 1149.10 reference design implemented in a FPGA demonstration vehicle for the V93000 system are presented.

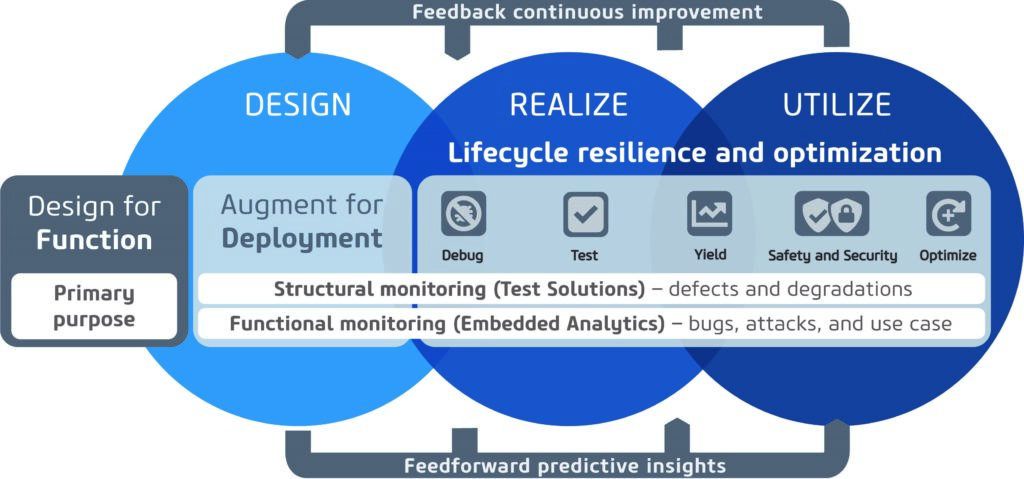

More on Silicon Lifecycle Solutions

Since the previous VOICE conference, Tessent became part of Siemens Digital Industries Software (Siemens EDA) and expanded our vision to include DFT, Operations, and Embedded Analytics. Together, these solutions enable a full Silicon Lifecycle Solutions (SLS) portfolio. The Tessent director of Operations products, Matt Knowles, will introduce the broader concepts of SLS and then focus on where the Operations products (Tessent Diagnosis, Tessent YieldInsight, and Tessent SiliconInsight) fit in this expanded environment.

More about using high-speed IOs/SERDES for scan test with IEEE 1149.10

Constant increases in design size is a perennial challenge for IC test. Controlling test costs as design sizes have grown exponentially has largely been possible due to improvements in test compression.

However, the number of pins accessible for scan test, GPIO pins, is not growing because ICs need more and more high-speed pins. A holy grail in IC test is therefore to re-use high speed IOs (called HSIOs or SERDES) for scan test. Making this a reality required a solution that would work with the existing tester hardware and not impact the IO design or functional operation of the chip.

The industry rallied around the challenge, and Siemens Tessent along with Advantest and others developed an end-to-end solution based on IEEE 1149.10 standard for re-using high speed IOs for scan test. IEEE 1149.10, approved in May 2017, defines circuitry for testing ICs through a high-speed TAP with a packet encoder/decoder and distribution architecture through which instructions and test data are communicated. This approach has several advantages, including maintaining testability of the functional path, and being future-proof against future functional high-speed protocols.

Register now for VOICE and tune into our presentation and a demonstration from Advantest to learn about using HSIOs for scan test.