Accelerating TRNG Verification: Microsoft-Siemens EDA Breakthrough Simulation Methodology at DAC

From 1.5-year simulation bottlenecks to verification in days, Microsoft and Siemens EDA’s collaboration presented at the Design Automation Conference (DAC) eliminates one of the biggest roadblocks in hardware security verification.

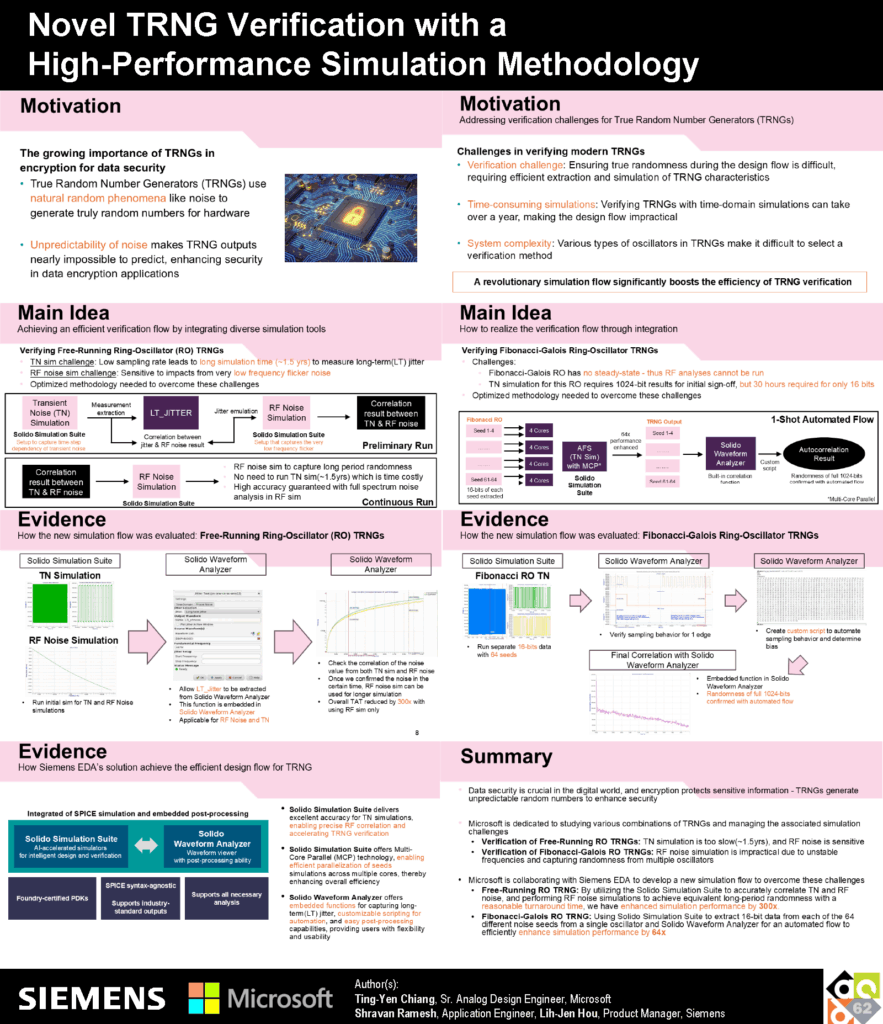

The TRNG verification challenge in hardware security

If you have ever worked on hardware security, you know the TRNG verification challenge: simulations that can stretch beyond a year.

True Random Number Generators (TRNGs) are essential; they use natural random phenomena like noise to generate truly unpredictable random number sequences that make encryption nearly impossible to crack. But there are complex design verification challenges: traditional time-domain simulations can take over a year to verify true randomness, and different TRNG architectures like Free-Running Ring-Oscillator (RO) and Fibonacci-Galois RO each present unique verification obstacles. Historically, these time-consuming simulations have made the design and verification flow impractical and created major bottlenecks in secure hardware development.

At DAC, Microsoft and Siemens EDA presented an innovative methodology to overcome these challenges. They demonstrated how to verify TRNG randomness with dramatically reduced simulation times while maintaining accuracy using Solido Simulation Suite. This collaboration transforms TRNG verification from impractical to achievable, making secure hardware development feasible within real-world timelines.

So how did they solve this? Two tailored approaches for two different TRNG architectures, each with its own headaches.

The presentation and associated poster highlighted specialized verification flows for Free-Running RO and Fibonacci-Galois RO TRNGs, each delivering dramatic performance improvements while ensuring rigorous randomness validation.

Free-Running RO TRNG verification flow

This methodology tackles a critical challenge: measuring long-term jitter in Free-Running Ring-Oscillator based TRNGs with low sampling rates traditionally requires long transient noise (TN) simulations that could take 1.5 years to complete. The solution correlates TN and radio frequency (RF) noise simulations using Solido Simulation Suite. By running preliminary TN and RF Noise simulations to establish correlation, then using RF Noise simulation alone for long-term jitter capture, designers bypass the time-costly TN simulation entirely. Solido Waveform Analyzer’s embedded long-term jitter extraction function enables accurate verification with full spectrum noise analysis.

💡Key takeaway: 300X performance enhancement: reducing 1.5-year TN simulations through correlated RF Noise methodology that eliminates time-costly transient analysis.

Fibonacci-Galois RO TRNG verification flow

In this flow, the challenge is even more complex: Fibonacci-Galois RO has no steady-state, making RF analysis impossible, and TN simulation requires 1024-bit results for initial sign-off but takes 30 hours for only 16 bits.

The optimized methodology uses an automated one-shot flow that extracts 16 bits from each of the 64 different noise seeds using Solido Simulation Suite. Solido Waveform Analyzer’s built-in correlation function and custom scripting capabilities automate the entire process, confirming randomness of the full 1024 bits through efficient parallelization.

💡Key takeaway: 64X performance enhancement through automated multi-core verification across 64 noise seeds with integrated post-processing.

Real-world impact: faster, practical TRNG verification

By reducing simulation times from over a year to days, design teams can complete verification within reasonable development cycles. The ability to handle different TRNG architectures, from Free-Running RO with its long-term jitter challenges to Fibonacci-Galois RO with its unstable frequencies and multiple oscillators, means teams can verify various TRNG designs efficiently.

The bottom line? Teams can now verify different TRNG designs without waiting over a year. That’s the difference between a theoretical security feature and one you can actually ship!

This presentation and poster were developed by:

- Ting-Yen Chiang, Principal Design Engineer, Microsoft

- Shravan Ramesh, Application Engineer, Siemens EDA

- Lih-Jen Hou, Product Manager, Siemens EDA

Want more details?

View the full technical poster to explore how Solido Simulation Suite’s AI-accelerated simulators, multi-core parallel technology, and Solido Waveform Analyzer can transform your TRNG verification workflow and overcome complex verification challenges in secure hardware design.