First out of the (3DIC) box: How Siemens EDA is using the TSMC 3Dblox standard to change 3DIC verification

By John Ferguson

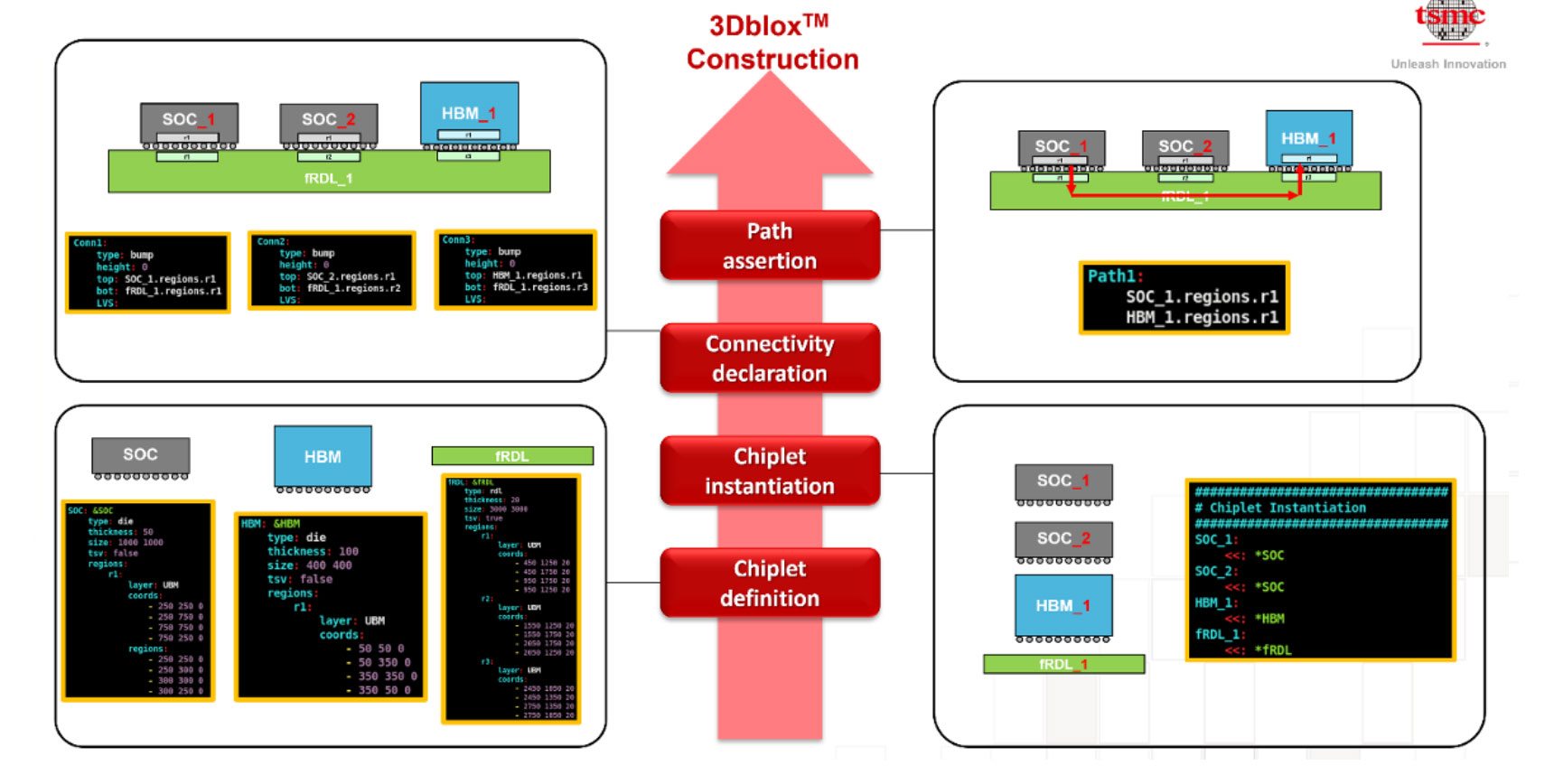

In recognition of the growing need for a more holistic approach to three-dimensional integrated circuit (3DIC) design, TSMC introduced their 3DFabric™ technologies in 2020 to incorporate system design, 3D stacking, and their advanced packaging technologies, such as TSMC-SoIC™, InFO, and CoWoS®. That was quickly followed by the formation of the TSMC Open Innovation Platform® (OIP) 3DFabric Alliance to accelerate 3DIC ecosystem innovation and readiness even further. To kickstart that innovation, TSMC introduced the TSMC 3Dblox™ standard, a new open standard language intended to simplify the design of 3DICs for TSMC customers. In recognition of the reality that 3DIC design requires inputs from a variety of ecosystem partners, TSMC chose to open the 3Dblox format to anyone in the industry, including competing foundries or package houses. The 3Dblox format can be used for every aspect of 3DIC design, including physical implementation, timing verification, physical verification, electromigration and voltage (IR) drop (EMIR) analysis, thermal analysis, and more. The 3Dblox language was designed to fulfill three goals:

- Provide a uniform generic format that can be used by all EDA tools to describe the key physical stacking and the logical connectivity information in 3DIC designs, making tool interoperability across any supported tools, as well as integrating data from multiple parties into a comprehensive 3DIC design, a breeze.

- Modularize 3DIC structures to simplify the 3DIC design flow and enable EDA tools to be more efficient and user-friendly

- Ensure that all EDA tools and design flows that employ the 3Dblox format are compliant with all TSMC 3DFabric technologies

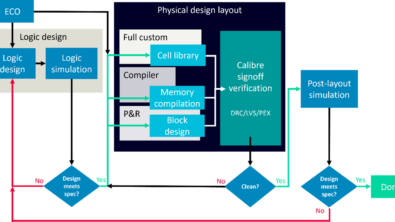

In the domain of 3DIC physical and circuit verification, the biggest hurdle has been the challenge arising from the simple fact that users can make independent choices of chiplet and processes to include into a 3DIC design. This freedom of choice makes it all but impossible to have a traditional verification deck that can run on any 3DIC design, since only the designer knows what is in that design. Siemens EDA Xpedition™ Substrate Integrator and Calibre® 3DSTACK tools have been providing a heterogeneous package assembly verification flow for several years now, and are proven in multiple production environments. With the availability of the TSMC 3Dblox standard language, and our long-history of collaboration with TSMC, we were able to quickly embrace the benefits to enable the development of Calibre 3DSTACK decks to support the various TSMC 3DIC offerings. With standardized data, physical verification of a 3DIC design can now be largely automated, providing Calibre accuracy while remaining fully independent of the design flow or design tools used.

The availability of the 3Dblox language has also simplified other options in 3DIC verification, such as thermal analysis at the chip or IP level. Using a combination of Siemens EDA tools for detailed thermal analysis, 3DIC designers can determine how the package assembly, including heterogeneous chiplets, impact the electrical behavior of a specific chip. Outputs in the form of static or dynamic heat maps can be presented at the assembly, die, or IP level, and designers can generate a post-layout netlist with temperature coefficients associated on the devices, enabling accurate sign-off signal or timing analysis. Thermal results can also be passed back into the mPower™ tool for updating of the power analysis. Want to learn more about how Siemens EDA tools are already implementing the TSMC 3Dblox standard? Watch Simplified Physical Verification of 3DICs through 3Dblox, a talk presented by John Ferguson at the 2022 TSMC OIP conference.

Image source courtesy of TSMC.