SoC integration issues? Now you can find them earlier, and fix them faster

By Nermeen Hossam and John Ferguson – Mentor, A Siemens Business

Our Calibre Recon tool helps SoC teams quickly find and resolve integration issues early in the design cycle, without incurring long DRC runtimes or multiple DRC iterations.

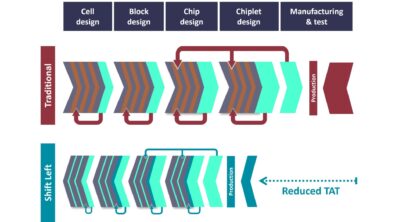

Finding and resolving integration issues in SoCs early in the design cycle is tough, time-consuming, and just plain impossible sometimes. Using the default settings in foundry rule decks for initial DRC runs typically results in very long runtimes, a massive number of reported violations, and an extremely large generated results database, all of which makes debugging extremely difficult and time-consuming. What if you could quickly find and fix integration issues in parallel with block development, while eliminating all those DRC iterations with their loooong runtimes? There’s a new tool in town that can help with that…

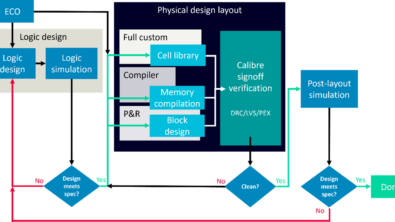

The Calibre™ Recon capability provides targeted checking that is very effective in identifying early potential integration issues and providing fast feedback to design teams for proper corrective actions. And, you can use it in conjunction with any foundry/independent device manufacturer (IDM) Calibre sign-off design kits “as is” on any process technology node.

How does it work? It automatically deselects checks that are not relevant for the current development phase. The Calibre engine makes the decision on which checks to deselect based on the check type, with the goal of providing good coverage, fast runtime, and less memory consumption. Of course, you can also manually deselect additional checks, if that makes sense for your design.

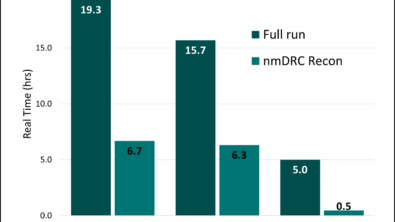

The result? Using the Calibre Recon tool reduces overall DRC runtime by up to 14x, while still checking ~50% of the total DRC set across a range of process nodes. Automatic deselection of checks typically results in the total number of reported violations being reduced to about 70% of the original count. Even better, though, is that the subset of rules automatically selected by the Calibre engine are effective in identifying floorplan and sub-chip integration issues, so these violations are more meaningful, helping you get right to analysis and debugging of real systematic issues.

Of course, there’s even more it can do, like supporting early block verification, and enabling you to check top-level routing while ignoring cell details. To get the full scoop, check out our white paper, Accelerate early design exploration & verification for faster time to market. The time you save may be the crucial market differentiator you were looking for.