Corporate

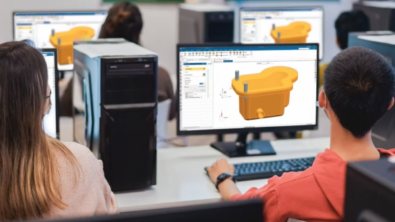

Free Classroom Resource: Introduction to SystemVerilog

If your senior undergraduate and graduate students of computer engineering, electronics and telecommunications are ready for a challenge in SystemVerilog, download this curriculum package today.

This course will try to cover the entire System Verilog language with examples that learners can connect the concepts with. It focuses on the key features of language and how to use them. Features include:

- Significant additions from Verilog

- What are they used for and how they are used

- Features that are useful for design and verification

- Lab exercises using Questa/ ModelSim

Note this is not a course on design or verification. A strong background in Digital Design and SystemVerilog HDL programming is recommended.

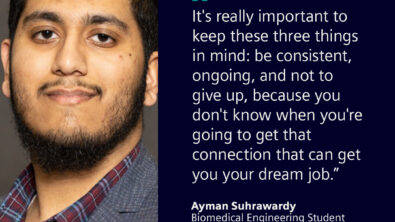

Check another one of our free classroom resources on emerging functional verification methods here.