Classroom Resource: Emerging Functional Verification Methods

Check out this brand new classroom resource on functional verification methods for senior undergraduate and graduate students of computer engineering, electronics and telecommunications.

Functional verification is the process of demonstrating the functional correctness of a design with respect to the design specifications. Functional verification does not confirm the correctness of the design specification and assumes that the design specification is correct. It is one of the most challenging steps of the IC design cycle, and is the main reason for IC re-spin.

This curriculum is an introduction to the theory and techniques to shift digital circuit design verification to earlier stages of development. Topics covered include:

- pre-silicon validation

- emulation

- formal verification

- system specification

- verification

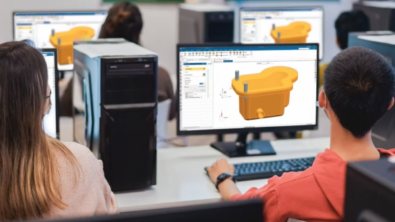

A design project is an integral part of this course. Students will gain experience using different techniques used to validate modern digital designs. The course will cover theory and methodology followed by hands on experience with emulation (Veloce) and formal methods. The course material complements other ECE pre-silicon and post-silicon functional validation courses.

It is suggested that students have prior experience in Veloce Emulation hardware, Strong Digital Design, Computer architecture, and HDL programming.

Click here to download the emerging functional verification methods curriculum!