Emulation and simulation; invaluable tools for IC verification

Emulation technology has been around for a long time—more than four decades by my count—and industry observers believe more than ever that it’s a key ingredient in the IC verification strategy, albeit with a rebirth. The question is, what is this new era of emulation all about and why is hardware emulation, which remained on the fringes of IC design ecosystem with a small customer base for many years, now becoming a mainstream design tool for system-on-chip (SoC) verification? The answer can be found in the advent of bigger and more complex chips that often contain multiple processor cores and exceed 100 million gates.

In a nutshell, a register-transfer-level (RTL) simulator, a go-to verification tool is being challenged as design capacity surpasses 100 million gates. Greater gate counts are possible because of the scaling roadmap for processors. After all, there is only so much you can do with multi-threading. Next, even hardware-description-language (HDL) software simulators running in parallel over PC farms don’t create a viable option because design-under-test (DUT) environments are sequential in nature.

On the other hand, hardware emulation, once the staple of large IC designs like processors and graphic chips, is now becoming a popular verification tool precisely because it runs faster than HDL simulators for full-chip verification. A hardware emulation tool can run the verification of large, SoC designs over 10 times and sometimes much greater than 10 times faster than software simulation.

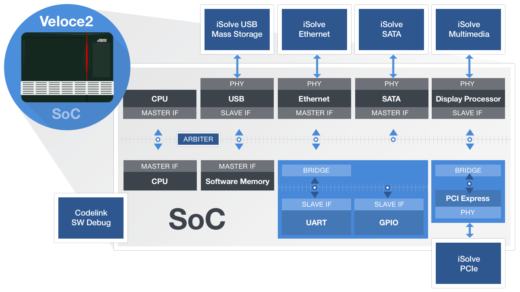

The view of the key verification modes supported by Mentor Graphics’ Veloce emulator platform.

Hardware emulation has been steadily evolving over the past decade or so, as the cost of ownership is coming down while emulation tools are becoming easier to install and operate. And with the changing equation of emulator ROI and SoC design imperatives, an increasing number of IC designers are inclined to use emulation tools for debugging the hardware and testing hardware and software integration. Moreover, emulation tools are becoming more versatile, ranging from in-circuit emulation (ICE), where physical devices are cabled to the emulator, to more innovative co-emulation solutions like Veloce VirtuaLAB that virtualizes the interfaces amid the growing functionality of today’s SoC designs.

Software simulation or hardware emulation

A simulator tries to model the behavior of the SoC or system-level design while an emulator creates an actual implementation of the design. Here, it’s important to note that both software simulators and hardware emulators are employed for design verification—a stage also known as design-under-test or DUT—where a compiler converts the design model into a data structure stored in memory.

However, in the case of simulation, a software algorithm processes the data representing a design model using a design language, while an emulator processes the data structure using a compute engine enabled by a processor array. Although hardware emulation is growing beyond a $300 million market, it doesn’t mean that it’s going to be the end of the road for HDL simulation tools.

The Veloce emulator, which supports both traditional ICE and transaction-based verification, runs verification of SoCs with multiple protocol interfaces.

HDL-based software simulation will most likely remain the verification engine of choice, especially at the early stage of verification process—for instance, at the IP and subsystem levels—as it represents an economical, easy-to-use, and quick-to-setup EDA tool. On the other hand, emulation will gain traction in larger SoC designs that encompass millions of verification cycles and where hardware bugs are difficult to find. In other words, the two EDA tool markets for SoC and system-level design verification will co-exist for the foreseeable future.

Comments