Supporting A Season of Learning

From those just beginning to study electronic systems design to the practicing engineer, this is the time of the year when those taking their first steps to learn VHDL, Verilog/SystemVerilog join the academic “back to school” crowd and those who are using design & verification languages in practice are honing skills at industry events around the world.

A new academic year has started and the Mentor Higher Education Program (HEP) is well set to help students at more than 1200 colleges and universities secure access to the same commercial tools and technology used by industry. It is a real win-win when students learn using the same tools they will use after graduating. Early exposure and use means better skilled and productive engineers for employers.

The functional verification team at Mentor Graphics knows that many students would prefer to have a local copy of ModelSim on their personal computer to do their course work and smaller projects as they learn VHDL or Verilog. To help facilitate that we make the ModelSim PE Student Edition available for download without charge. More than 10,000 students use ModelSim PE Student Edition around the world now in addition to our commercial grade tools they can access in their university labs.

For the practicing engineer, the Verification Academy offers an online community of more than 25,000 design and verification engineers that exchange ideas on a wide variety issues across the numerous standards and methodologies. If you are not a member of the Verification Academy, I recommend you join. You will also find the Verification Academy at DAC for one-on-one discussions and even more recently Verification Academy Live daylong seminars which came to Austin and which will be in Santa Clara – as of the writing of this blog. There is still time to register for the Santa Clara event and I invite you to attend.

As design and verification is global, Accellera realized that DVCon should explore the needs of the global design and verification engineer population as well. For 2014, DVCon Europe and DVCon India were born from an already successful running SystemC User Group events. These user-led conferences will be held so engineers in these areas can more easily come together to share experiences and knowledge to ultimately become more productive.

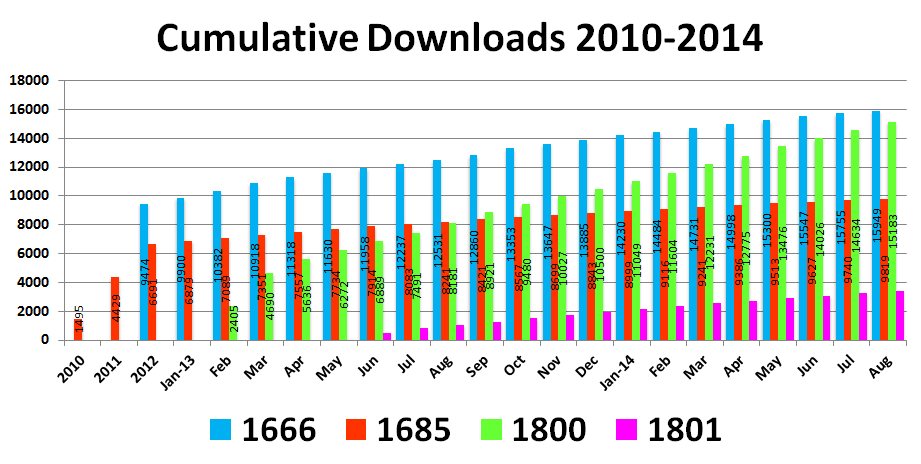

Students and practicing engineers alike can benefit from fee-free access to some of the popular IEEE EDA standards. While I don’t think reading them alone is the ultimate way to educate yourself, they make great companions to daily design and verification activities. Accellera has worked with the IEEE to place several EDA standards in the IEEE Standards Association’s “Get™” program. Almost 16,000 copies of the SystemC standard (1666) and just about the same number of SystemVerilog standards (1800) have been downloaded as of the end of August 2014. Have you download your free copies yet?

The chart below shows the distribution of nearly 45,000 downloads which have occurred since 2010. Stay tuned for breaking news on some updates to the EDA standards in the Get program. When updated, they will replace the versions available now. So if you want to have the current versions and the ones to come out shortly, you better download your copies now. If the electronic version is not sufficient for you, the IEEE continues to sell printed versions.

From students to practicing engineers, the season of learning has started. I encourage you to find your right venue or style of learning and connect with others to advance and improve your design and verification productivity.